Программное обеспечение для проектирования FPGA: обзор возможностей интеграции времени в проектный комплект Vivado Xilinx

В этой статье мы рассмотрим некоторые из наиболее важных функций Xilinx Vivado Design Suite, которые ускоряют «время интеграции» процедуры проектирования.

Традиционный дизайн FPGA в основном фокусируется на концепции программируемой логики и ввода-вывода. Однако современные сложные приложения требуют выхода за пределы программируемой логики к «программируемым системам». Это одна из самых фундаментальных идей создания Xilinx Vivado Design Suite.

Vivado - это IP-и системно-ориентированная среда проектирования, которая пытается упростить интеграцию мягких IP-адресов. Это достигается несколькими функциями, которые будут кратко рассмотрены в остальной части статьи.

Обратите внимание, что функции, описанные в этой статье, в основном направлены на ускорение «времени интеграции» процесса проектирования. В другой статье мы обсудим те особенности Vivado, которые намерены ускорить «время реализации» дизайна.

Расширение IP-репозитория Vivado

Vivado имеет расширяемый каталог IP, который может включать в себя Xilinx и сторонние IP-адреса. Vivado позволяет инженерам быстро превратить часть своего дизайна или алгоритма в повторно используемый IP-адрес, добавленный в каталог Vivado IP.

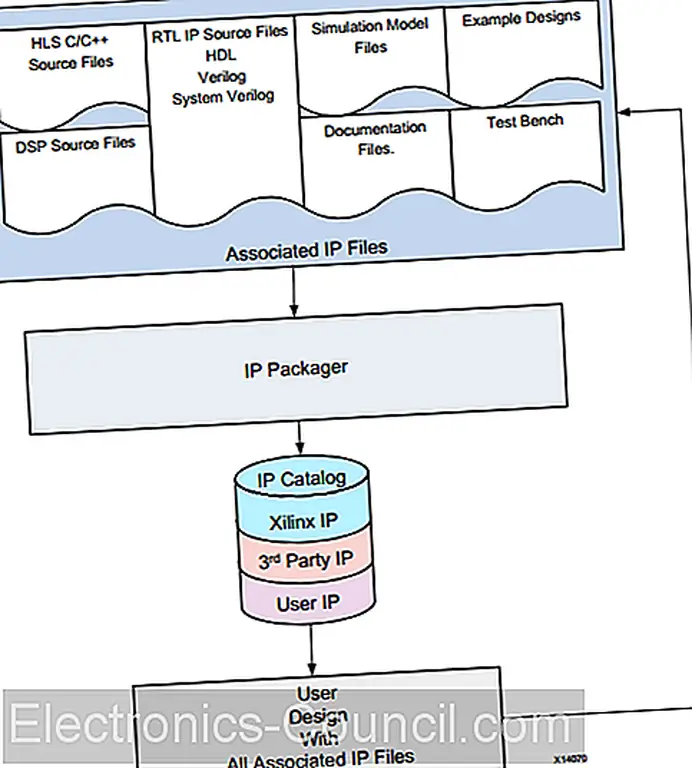

Как показано на рисунке 1, с Vivado IP Packager, все связанные файлы проекта, такие как ограничения, тестовые скамейки и документация, могут быть добавлены к созданному IP.

Рисунок 1. Поток создания Vivado IP. Изображение предоставлено Xilinx

Одной из важных особенностей потока Vivado IP является возможность создания IP-адреса на любом уровне дизайна, независимо от того, является ли он проектом уровня ретрансляции (RTL), списком соединений, размещенным списком соединений или даже размещенным, и маршрутизированный список соединений.

Также обратите внимание, что, как показано на рисунке 1, исходные файлы IP Packager могут включать в себя алгоритмы MATLAB / Simulink из Xilinx System Generator или C / C + / SystemC алгоритмы из Vivado High-Level Synthesis (HLS). В этих случаях запатентованное IP-поколение дополнительно ускоряется, потому что более высокий уровень описания используется для разработки целевого алгоритма. HLS будет кратко рассмотрен в следующем разделе.

C-Based IP Generation с Vivado HLS

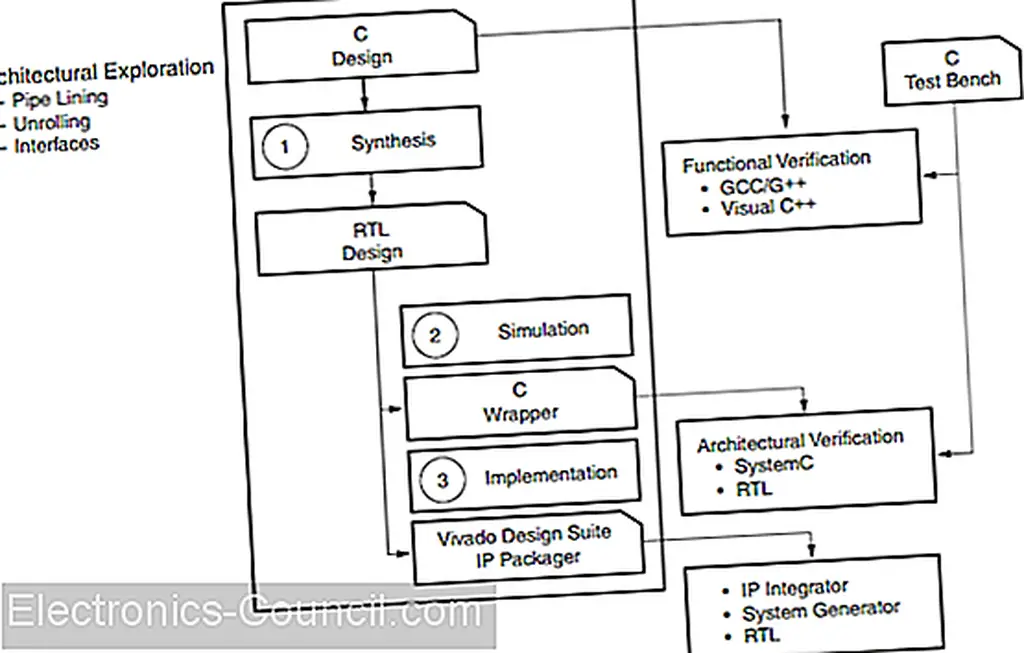

Разработка современных алгоритмов не является простой, даже для самых опытных команд RTL. Вот почему такие инструменты, как Vivado HLS, которые могут получать алгоритмы C / C + / SystemC и извлекать код VHDL или Verilog, могут значительно ускорить разработку IP и, следовательно, процесс проектирования.

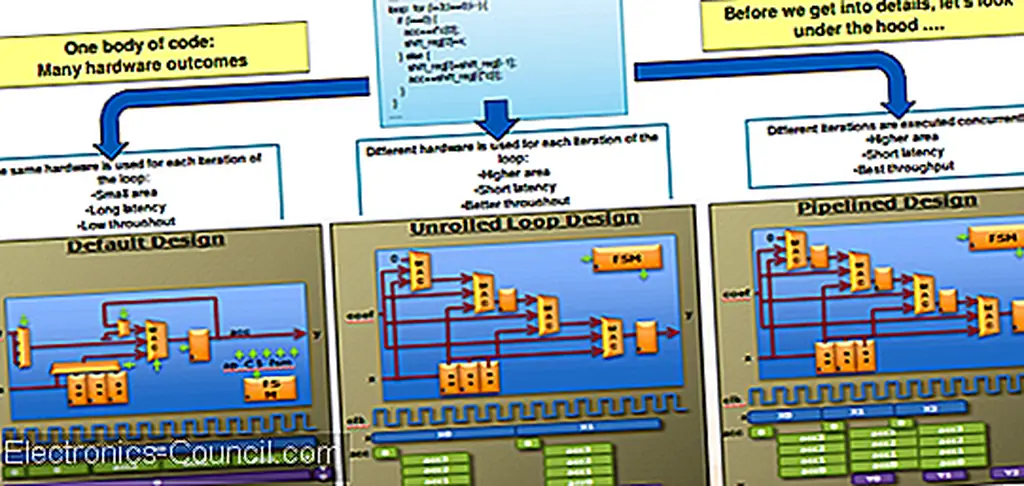

Vivado HLS позволяет инженеру исследовать пространство проектирования и находить несколько различных реализаций для того же исходного кода, как показано на рисунке 2 ниже.

Рисунок 2. Изучение проектного пространства с помощью HLS. Изображение предоставлено Xilinx

Как вы можете видеть, инструмент может оптимизировать несколько параметров проектирования, таких как площадь, латентность и пропускная способность.

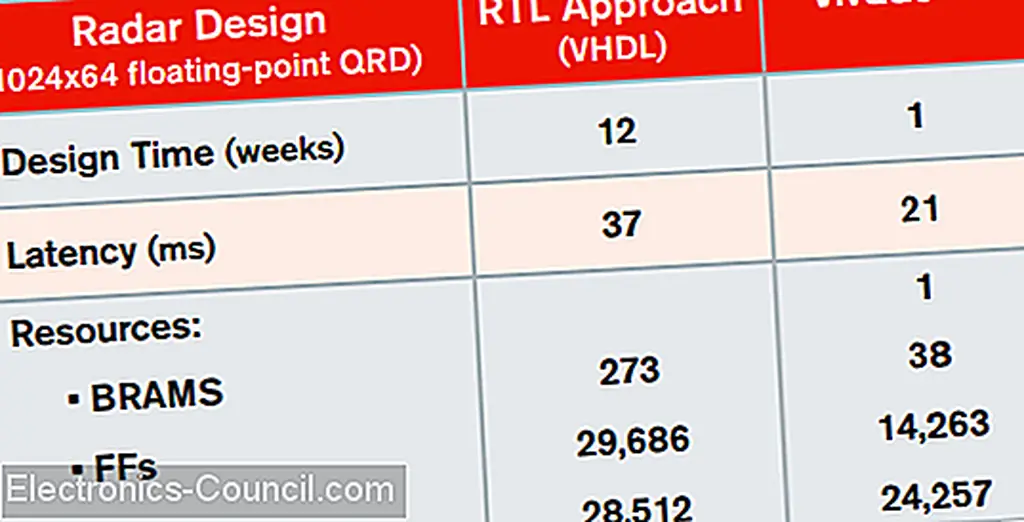

Также возможно, что инженер может использовать HLS, чтобы найти решение лучше, чем у RTL с ручным кодированием. На рисунке 3 ниже сравниваются результаты подхода RTL с примером HLS для примера проектирования радара.

Рисунок 3. Сравнение подхода RTL с HLS. Изображение предоставлено Xilinx

Для этого HLS фактически учитывает свойства целевого устройства, такие как доступные фрагменты DSP48, память и SRL. Он также пытается эффективно реализовать алгоритмы с плавающей запятой и автоматически извлекать параллелизм на разных уровнях.

Языки программирования высокого уровня, такие как C, могут быть чрезвычайно полезными и на этапе проверки алгоритмов. Дизайнер может быстро моделировать и повторять дизайн с использованием функциональных спецификаций C, а затем создавать целевую RTL-архитектуру. В примере видеопроекта модель C ускорила время проверки алгоритма примерно на 12 000 раз. Некоторые детали этого эксперимента показаны на рисунке 4 ниже.

Рисунок 4. Время моделирования для моделей RTL и C. Изображение предоставлено Xilinx

Поток дизайна Vivado HLS показан на рисунке 5.

Рисунок 5. Расчетный поток Vivado HLS. Изображение предоставлено Xilinx

Высокоуровневая системная интеграция

Теперь, когда у нас есть решения для быстрого создания необходимых IP-адресов, разумно подумать о методах быстрого подключения этих IP-адресов друг к другу. Чтобы это стало возможным, Vivado имеет IP Integrator (IPI), который позволяет пользователю графически описывать соединения между IP-адресами.

Дизайнер может создавать соединения на уровне интерфейса или уровне порта. Выбор работы на уровне интерфейса позволяет группировать большое количество отдельных сигналов, которые используются для общей функции, и легко манипулировать ими.

Например, можно использовать одно соединение для подключения всех сигналов интерфейса. В качестве альтернативы, возможность проверки правил проектирования (DRC) инструмента может гарантировать правильность соединений интерфейса. Следовательно, дизайн будет правильным по конструкции. Такие DRC на сложных интерфейсах могут значительно ускорить этап проектирования.

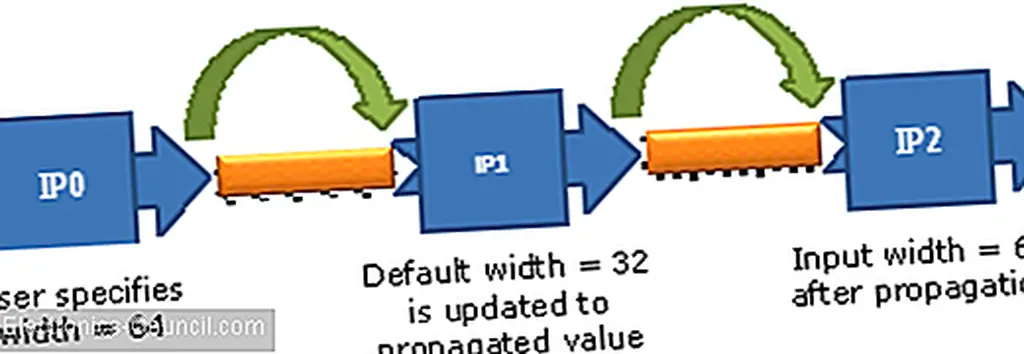

В дополнение к интеллектуальному автоматическому подключению ключевых IP-интерфейсов IPI поддерживает распространение параметров между подключенными IP-адресами. Концепция распространения параметров IP показана на рисунке 6.

Рисунок 6. Распространение параметров IP. Изображение предоставлено Xilinx

Предположим, что ширина шины данных IP1 имеет значение по умолчанию 32 бита. Теперь предположим, что пользователь подключает IP1 к IP0, который имеет ширину шины 64 бит. В этом случае правила распространения параметров инструмента могут обнаружить, что ширина шины изменилась. Пользователь может либо разрешить IPI автоматически обновлять ширину шины IP, либо направлять программу, чтобы просто отображать ошибку в качестве предупреждения о потенциальных проблемах в дизайне.

В этой статье вкратце рассмотрены некоторые функции FPGA для дизайна Vivado Design Suite. Если вы знакомы с аналогичными возможностями в других инструментах, пожалуйста, поделитесь своим опытом с нами в комментариях ниже.