Встраиваемая FPGA: меняются пути чипов

Узнайте, как работают встроенные FPGA и какие преимущества они предлагают.

Одной из наиболее важных проблем, с которой сталкиваются разработчики чипов сегодня, является необходимость переконфигурировать RTL в любой момент процесса проектирования, даже в системе. К сожалению, разработчики чипов не знают, нужно ли им это делать, пока не станет слишком поздно. Любые изменения на тот момент в конечном итоге стоят миллионы долларов и откладывают проекты по месяцам.

Со встроенной FPGA эта проблема уходит. Дизайнеры чипов могут, наконец, войти в проект, зная, что у них есть гибкость в изменении RTL в любое время во время проекта, чего раньше никогда не было.

Поскольку встроенная FPGA - это новая технология, мы сначала остановимся на том, как она отличается от стандартных FPGA, которые существуют уже несколько десятилетий. В принципе, встроенная FPGA представляет собой IP-блок, который позволяет включать FPGA в состав SoC или любой интегральной схемы. Так же, как RAM, SERDES, PLL и процессоры перешли от автономных чипов к обычным блокам IP, FPGA теперь также является IP-блоком.

FPGA объединяет массив программируемых / реконфигурируемых логических блоков в программируемой соединительной ткани. В микросхеме FPGA внешний край чипа состоит из комбинации GPIO, SERDES и специализированных PHY, таких как DDR3 / 4. В расширенных ПЛИС кольцо ввода / вывода составляет примерно 1/4 от микросхемы, а «ткань» составляет примерно 3/4 от микросхемы. Сама «ткань» в основном является межсоединением в сегодняшних чипах FPGA, где 20-25% площади ткани является программируемой логикой, а 75-80% - программируемым межсоединением.

Встроенная FPGA - это FPGA-ткань без окружающего кольца GPIO, SERDES и PHY. Вместо этого встроенная FPGA подключается к остальной части чипа, используя стандартную цифровую сигнализацию, обеспечивая очень широкие и очень быстрые межкомпонентные соединения.

Внутри встроенного FPGA: примитивные строительные блоки

Программируемый логический блок в FPGA является Look Up Table (LUT), который может реализовать любую логическую функцию через программирование: 4, 5 или 6 входов с одним или двумя выходами.

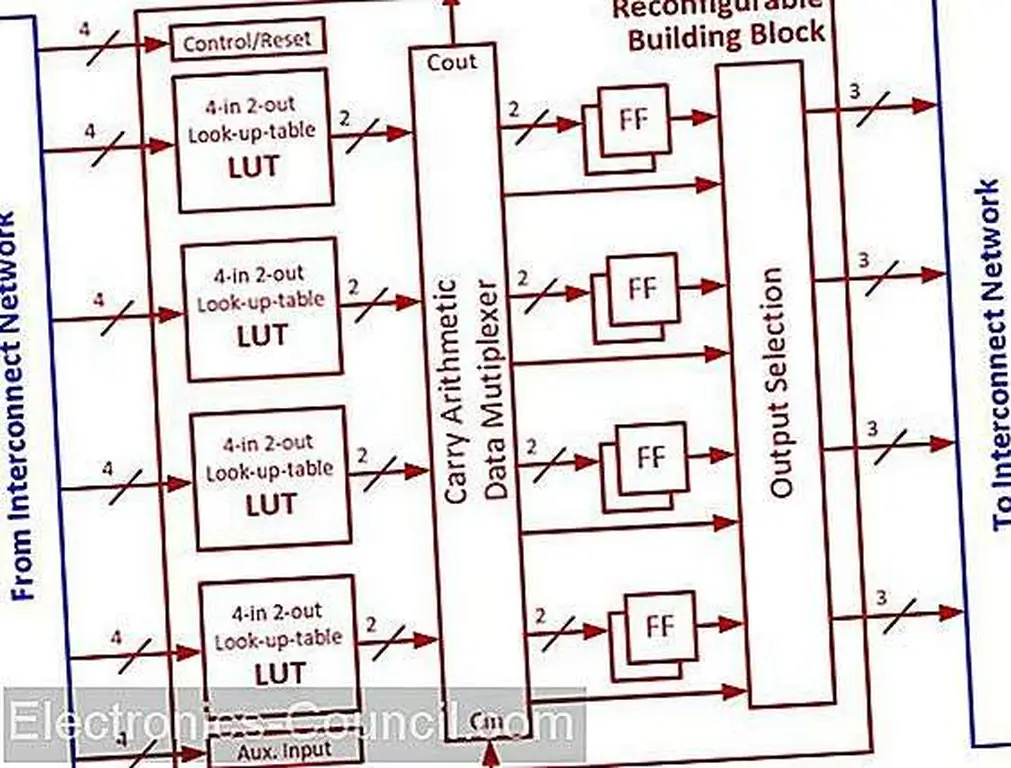

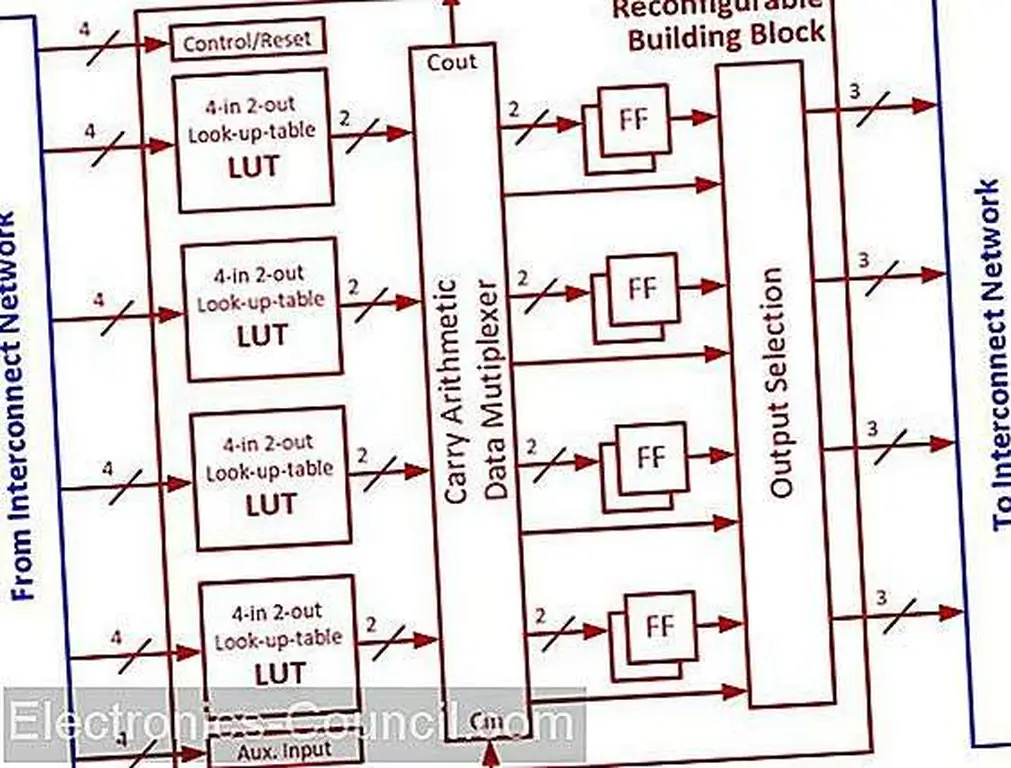

В массивах Flex Logix EFLX LUT представляет собой двойной 4-входной LUT, который можно комбинировать для формирования 5-входного LUT. Выходы LUT опционально можно хранить в триггерах. LUT обычно группируются в группы по четыре с логикой переноса для облегчения сумматоров и переключателей.

Другим программируемым логическим блоком является MAC (умножитель-аккумулятор) или блок ускорителя DSP.

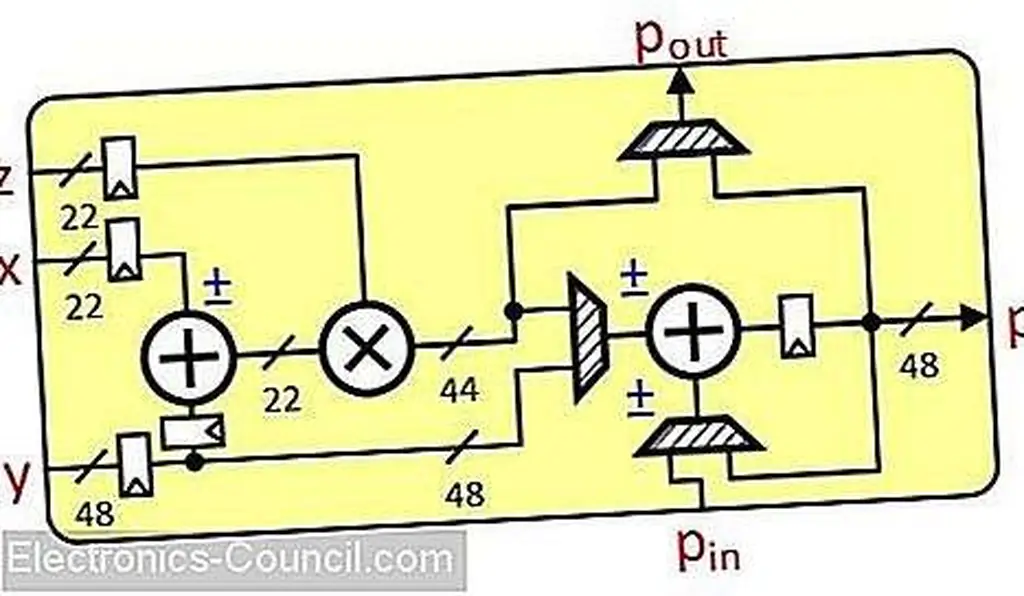

В массиве Flex Logix EFLX имеется 22-битный предварительный сумматор, множитель 22x22 и 4-разрядный пост-сумматор / аккумулятор. MAC могут быть объединены или каскадированы для создания быстрых функций DSP.

Программируемые логические блоки программируются битами конфигурации, которые устанавливают значения LUT, выбирают, используются ли триггеры, активируются или не выполняются логика переноса и т. Д. Биты конфигурации также программируют работу MAC. Обычно в FPGA биты конфигурации загружаются из внешней вспышки.

Для встроенных FPGA это одно и то же, поскольку почти все SoC имеют ARM / ARC / MIPS / и т. Д. процессор, который загружается из внешней вспышки. Эта же вспышка используется для хранения бит конфигурации для встроенной вспышки.

Программируемые логические блоки принимают входные сигналы и отправляют выходы в сеть межсоединений, что позволяет программировать соединения и любые логические блоки в FPGA-матрице. Соединительная ткань также программируется конфигурационными битами. Соединительная ткань обычно является основной частью ткани FPGA.

Основным отличием для встроенных FPGA является дизайн соединительной ткани. Лучшее межсоединение использует меньшую площадь и меньшее количество слоев металла, обеспечивая при этом высокую эффективность использования ресурсов.

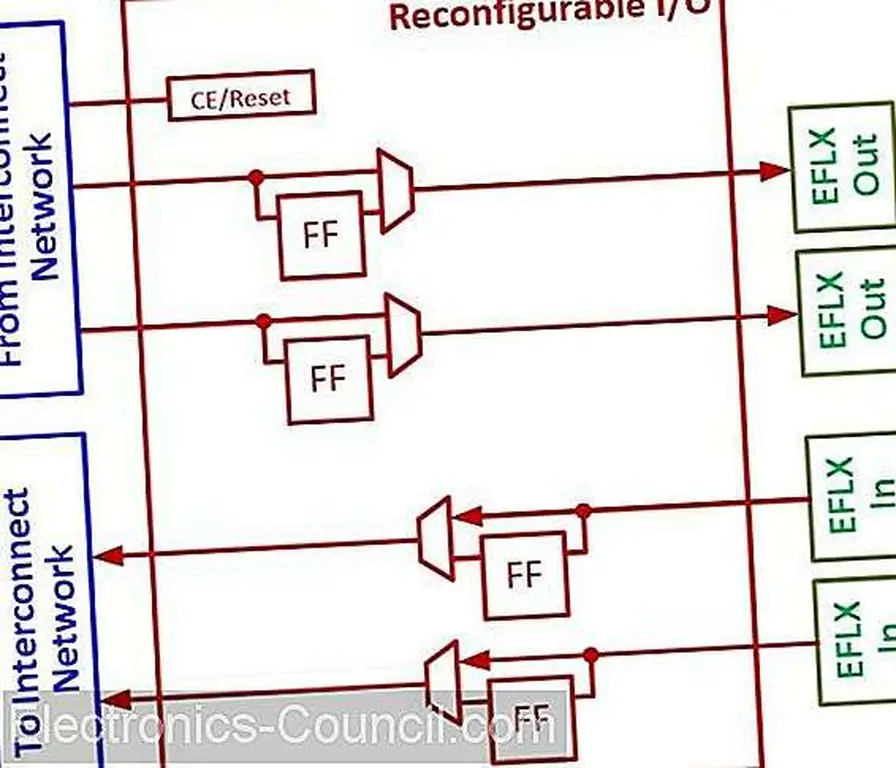

В отличие от микросхемы FPGA, во встроенной FPGA нет PHY / SERDES / PLL. Существует кольцо «I / O», но это действительно простые цифровые соединения с остальной частью чипа. Встроенная FPGA будет иметь от сотен до тысяч межсоединений, которые могут работать на полной скорости внутри чипа. Это увеличение ширины и пропускной способности ввода-вывода является огромным преимуществом внедрения FPGA в чипе.

Внутри встроенного FPGA: создание любого размера и конфигурации массива

Одна сложность заключается в том, что клиенты хотят иметь широкий диапазон размеров и конфигураций встроенных FPGA, и каждый хочет, чтобы IP-блок был доказан в кремнии, прежде чем использовать его в своем чипе.

Например, в 16 нм один клиент может потребовать всего несколько сотен LUT программируемой логики для быстрой реконфигурируемой логики управления, работающей на ~ 1 ГГц; в то время как другой клиент в том же процессе может захотеть 50 тыс. КБ для LAT для ускорителя процессора центров обработки данных. Как эти клиенты могут быть удовлетворены наименьшим количеством инвестиций в дизайн и время выхода на рынок »« src = »// www.allaboutcircuits.com/uploads/articles/image03.jpg» />

Каждое ядро EFLX IP имеет дополнительный верхний слой межсоединения, который позволяет одному ядру автоматически подключаться к окружающим соседям, чтобы сделать большой массив до NxN.

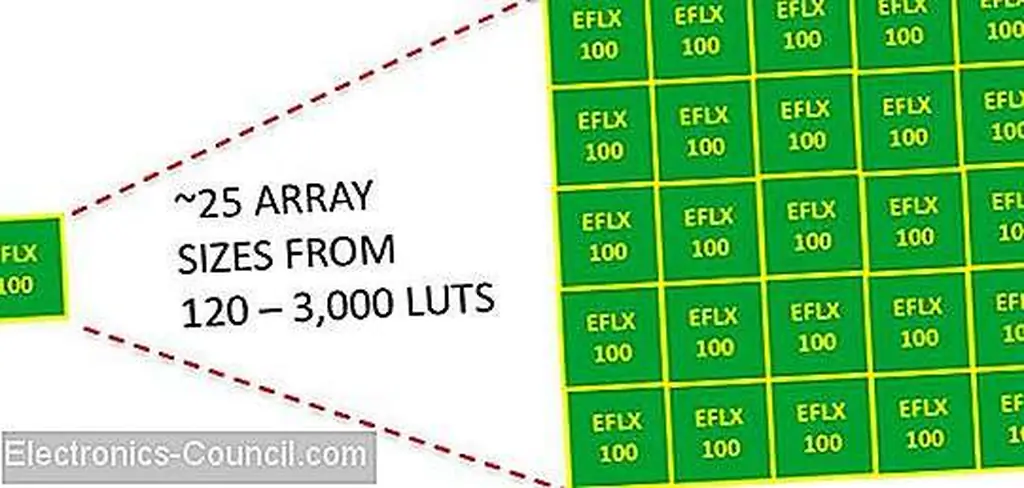

Массивы EFLX-100 до 5x5 или 3000 LUT (в EFLX-100 на самом деле 120 LUT).

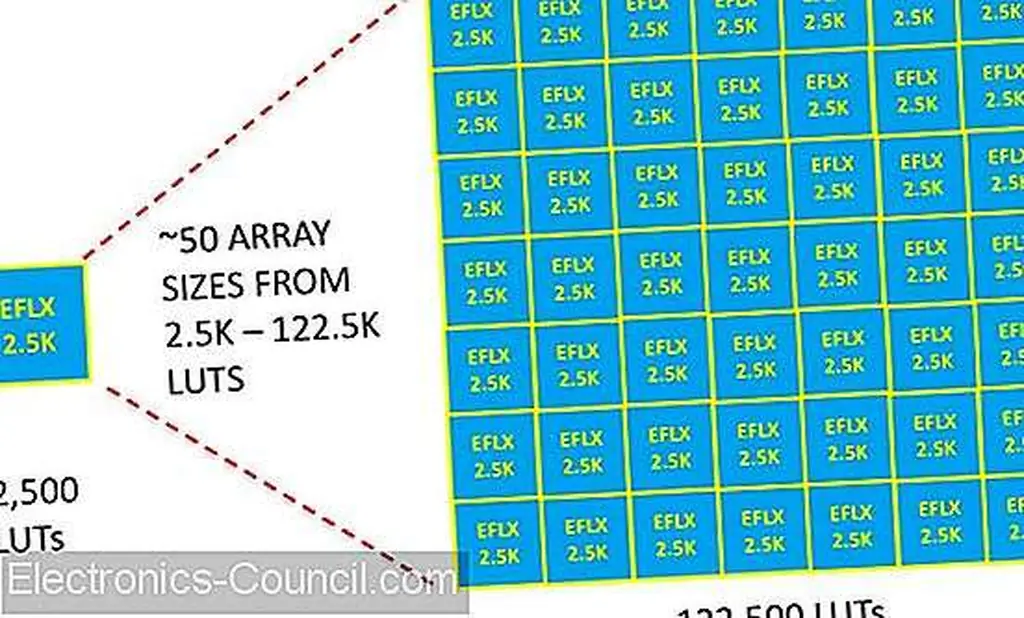

EFLX-2.5K берет на себя 2500 LUT и массивов до 122.5K LUT.

Массив может быть полностью логическим или полностью DSP или любым сочетанием двух типов ядер, например:

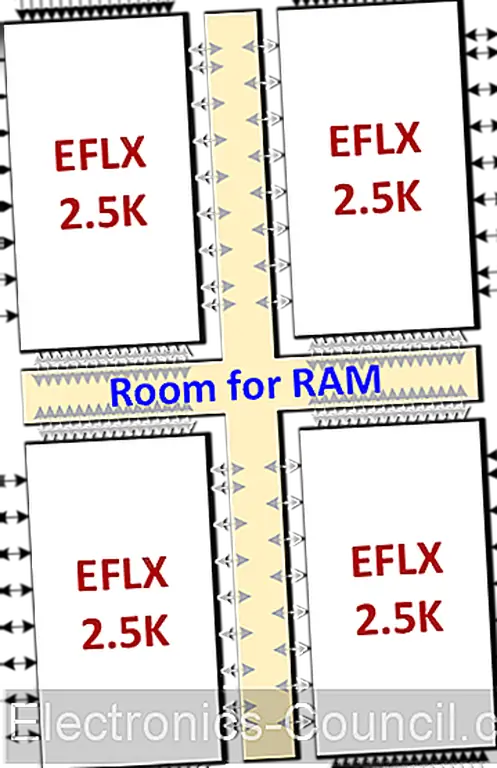

Также возможно встроить большие объемы ОЗУ во встроенный массив. Flex Logix делает это, используя стандартные компиляторы RAM для создания любого вида ОЗУ, которое запрашивает клиент (один порт, двойной порт, ECC / четность / нет, сколько угодно) и размещает ОЗУ между ядрами. ОЗУ является частью одного массива EFLX.

Использование вышеуказанного подхода позволяет нескольким IP-ядрам генерировать почти неограниченное множество встроенных массивов FPGA в соответствии с требованиями заказчика.

Внутри встроенного FPGA: доказательство строительных блоков в кремнии

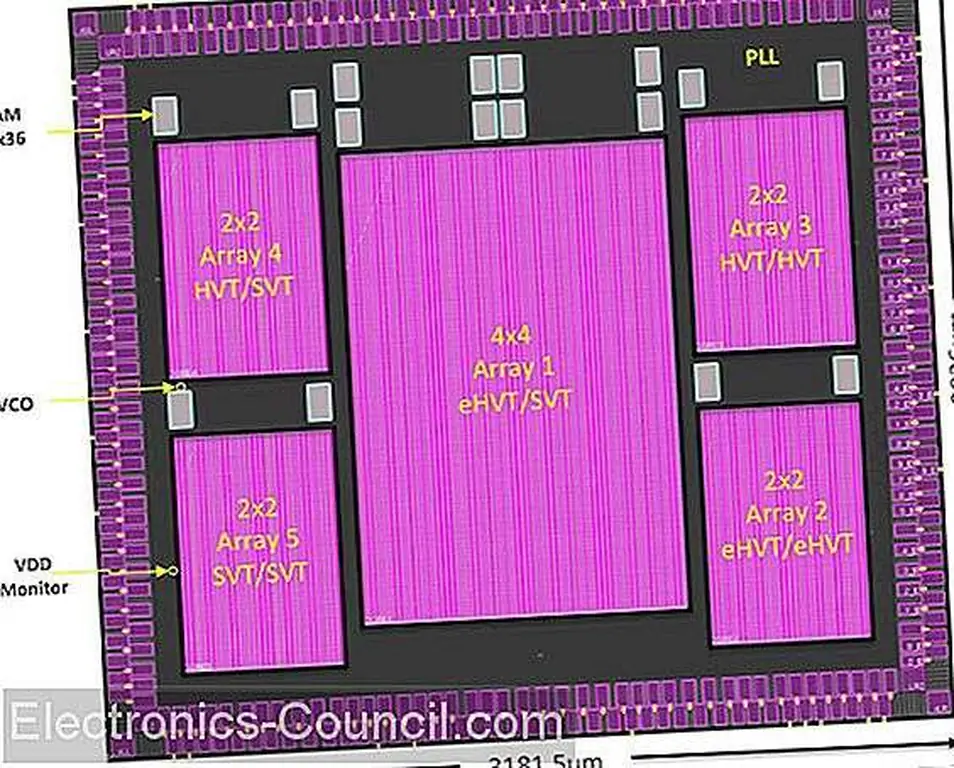

Flex Logix строит чипы проверки, чтобы проверить IP-сердечники в кремнии. Ниже приведен пример в TSMC 40ULP.

В этом процессе существует широкий диапазон комбинаций VT (маска порога напряжения), которые клиенты используют, и Flex Logix спроектировал массив EFLX для совместимости со всеми возможными комбинациями. Таким образом, чип проверки имеет пять массивов: один большой массив (4x4) в наиболее востребованной комбинации VT и четыре массива 2x2 в четырех других размерах.

Поскольку массивы EFLX в 40 нм могут работать до 300 МГц, а GPIO является только надежным до ~ 150 МГц, есть встроенная PLL для генерации очень быстрых точных часов для тестирования производительности, и существует SRAM, позволяющая банкам «тестовых векторов» «загружаться, а затем запускаться на полной скорости с выходом результатов в другой банк. Это дает «тестер на чипе», так что полная скорость работы может быть проверена на вышеуказанных скоростях GPIO. Существуют также мониторы температуры / напряжения, чтобы гарантировать, что тесты проводятся в целевых, худших условиях.

Вывод

Встроенная FPGA изменит способ разработки микросхем и SoC в будущем. Дизайнерам больше не нужно запираться в проекте и вынуждать тратить миллионы долларов на изменение RTL, если это необходимо. Компании также больше не должны рисковать отсутствием своих графиков, когда RTL необходимо обновить. Со встроенным FPGA процесс проектирования чипов просто стал намного проще и намного дешевле.

Отраслевые статьи - это форма контента, которая позволяет отраслевым партнерам делиться полезными новостями, сообщениями и технологиями с читателями All About Circuits таким образом, что редакционный контент не очень подходит. Все отраслевые статьи подчиняются строгим редакционным правилам с целью предоставления читателям полезных новостей, технических знаний или историй. Точки зрения и мнения, выраженные в отраслевых статьях, являются точками партнера, а не обязательно для All About Circuits или его авторов.