Устранение неполадок с основными логическими воротами

Цифровые схемы

Вопрос 1

Счетная практика: подсчет от нуля до тридцати одного в двоичном, восьмеричном и шестнадцатеричном:

|

|

Показать ответ

Здесь нет ответов - сравните с вашими одноклассниками!

Заметки:

Чтобы ознакомить студентов с этими «странными» системами нумерации, мне нравится начинать каждый день цифровой схемы с помощью практики подсчета. Студенты должны свободно владеть этими системами нумерации к тому времени, когда они закончат изучение цифровых схем!

Одно из предложений, которое я даю учащимся, чтобы помочь им увидеть шаблоны в последовательностях подсчета, - это «pad» числа с ведущими нулями, так что все числа имеют одинаковое количество символов. Например, вместо записи «10» для двоичного числа два, напишите «00010». Таким образом, становится очевидным, что характер цикличности символов (особенно двоичный, где каждый бит с более высоким значением имеет половину частоты одного перед ним) становится более очевидным.

вопрос 2

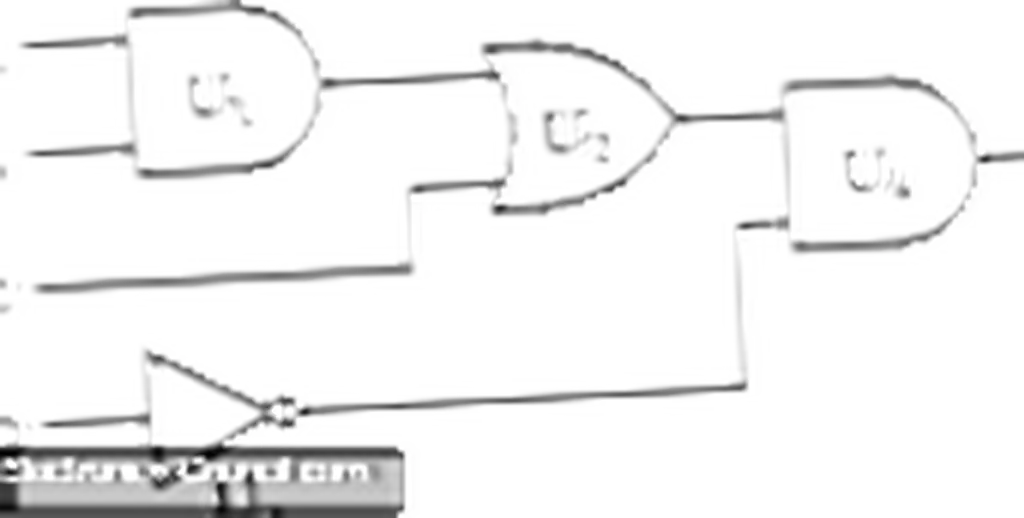

Предскажите, как будет затронута работа этой логической схемы ворот в результате следующих сбоев. Рассматривайте каждую ошибку независимо (т.е. по одному, без кратных ошибок):

|

|

- Вывод логического элемента U U 2 не работает:

- Выход инвертора U 3 не работает:

- Выход И ворот U 1 выходит из строя:

Для каждого из этих условий объясните, почему возникнут результирующие эффекты.

Показать ответ

- Вывод логического элемента U U 2 не работает: выход Gate U 4 застрял в низком состоянии.

- Выход инвертора U 3 выходит из строя низко: выход Gate U 4 застрял в низком состоянии.

- Выход И-выхода U 1 не может быть высоким: выход Gate U 4 просто равен (D), никакие другие входы не влияют на выход U 4.

Заметки:

Цель этого вопроса заключается в том, чтобы подойти к области устранения неисправностей схемы с точки зрения понимания того, что такое ошибка, а не только знать, что такое симптомы. Хотя это не обязательно реалистичная перспектива, это помогает студентам создавать фундаментальные знания, необходимые для диагностики неисправной схемы из эмпирических данных. Такие вопросы должны сопровождаться (в конечном итоге) другими вопросами, которые задают учащимся определение вероятных ошибок на основе измерений.

Вопрос 3

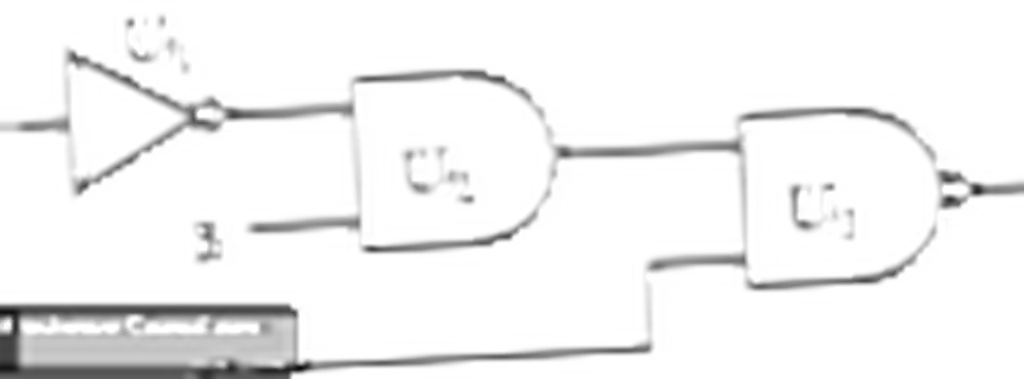

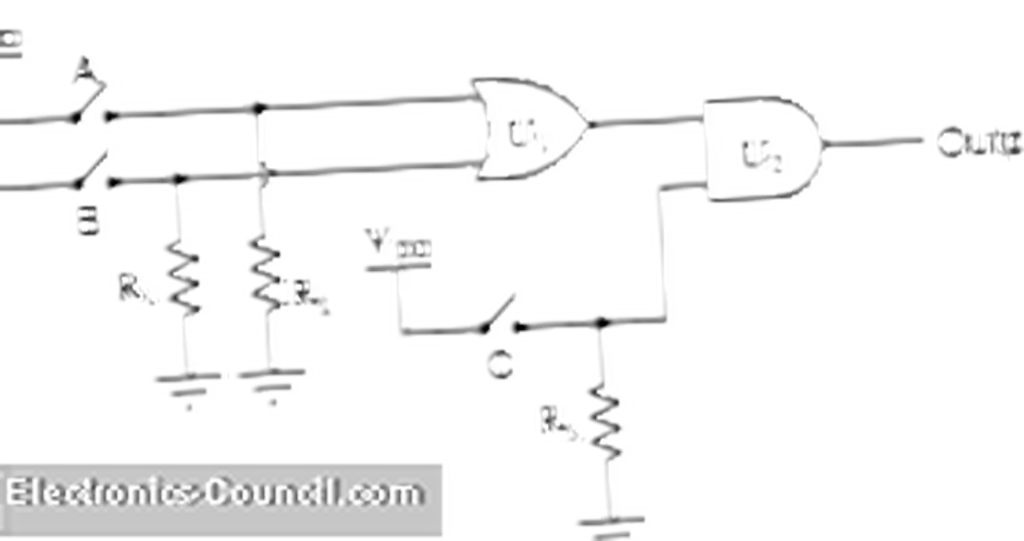

Предскажите, как будет затронута работа этой логической схемы ворот в результате следующих сбоев. Рассматривайте каждую ошибку независимо (т.е. по одному, без кратных ошибок):

|

|

- Выход И-выхода U 2 не работает:

- Выход И ворот U 2 не может быть высоким:

- Выход инвертора U 1 не работает:

Для каждого из этих условий объясните, почему возникнут результирующие эффекты.

Показать ответ

- Выход И ворот U 2 выходит из строя низко: выход Gate U 3 застрял в высоком состоянии.

- Выход И-выхода U 2 выходит из строя высоко: выход Gate U 3 просто равен (C), никакие другие входы не влияют на выход U 3.

- Выход инвертора U 1 не работает: выход Gate U 3 застрял в высоком состоянии.

Заметки:

Цель этого вопроса заключается в том, чтобы подойти к области устранения неисправностей схемы с точки зрения понимания того, что такое ошибка, а не только знать, что такое симптомы. Хотя это не обязательно реалистичная перспектива, это помогает студентам создавать фундаментальные знания, необходимые для диагностики неисправной схемы из эмпирических данных. Такие вопросы должны сопровождаться (в конечном итоге) другими вопросами, которые задают учащимся определение вероятных ошибок на основе измерений.

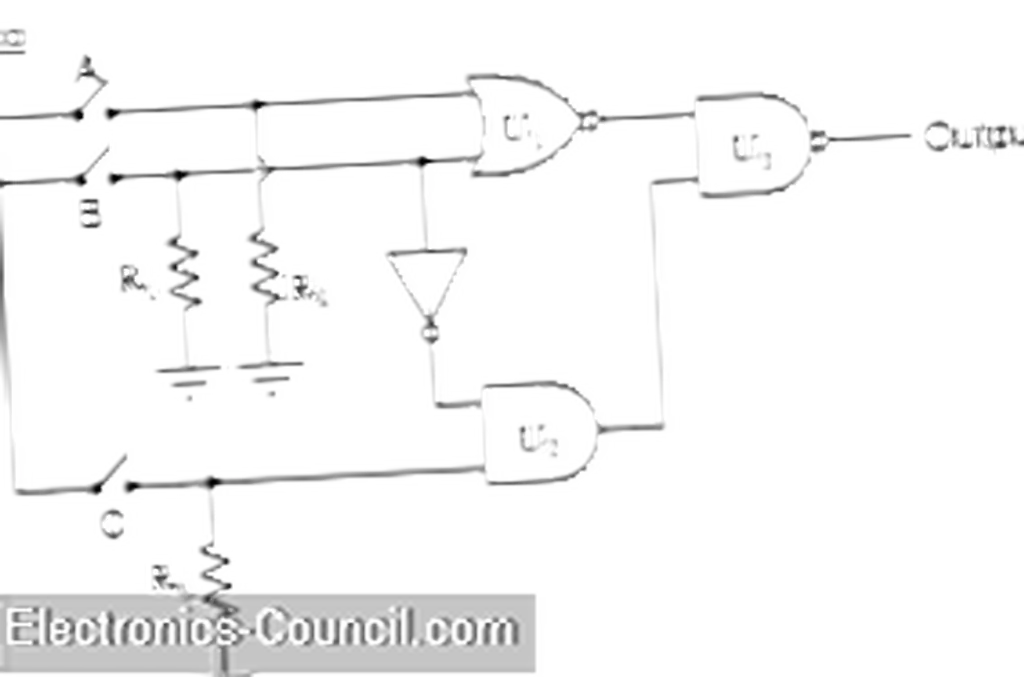

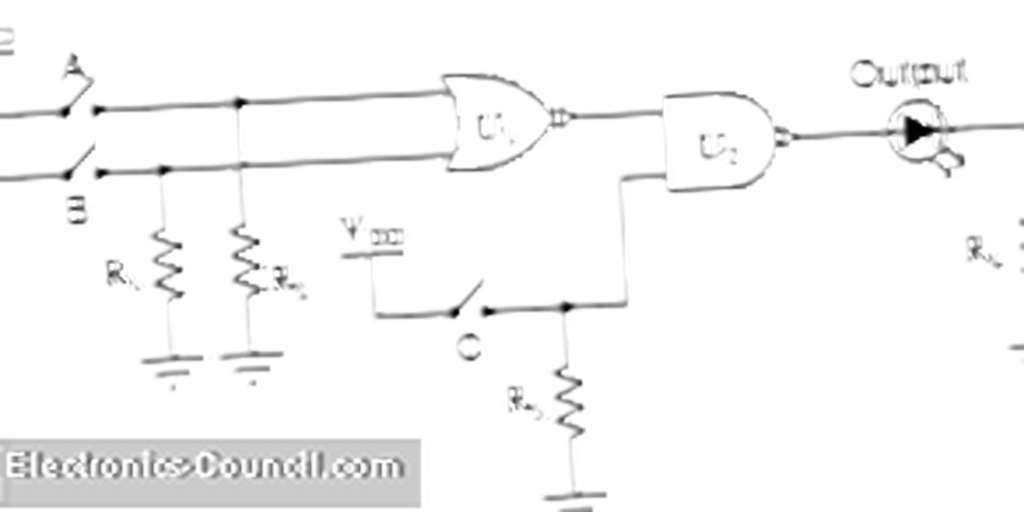

Вопрос 4

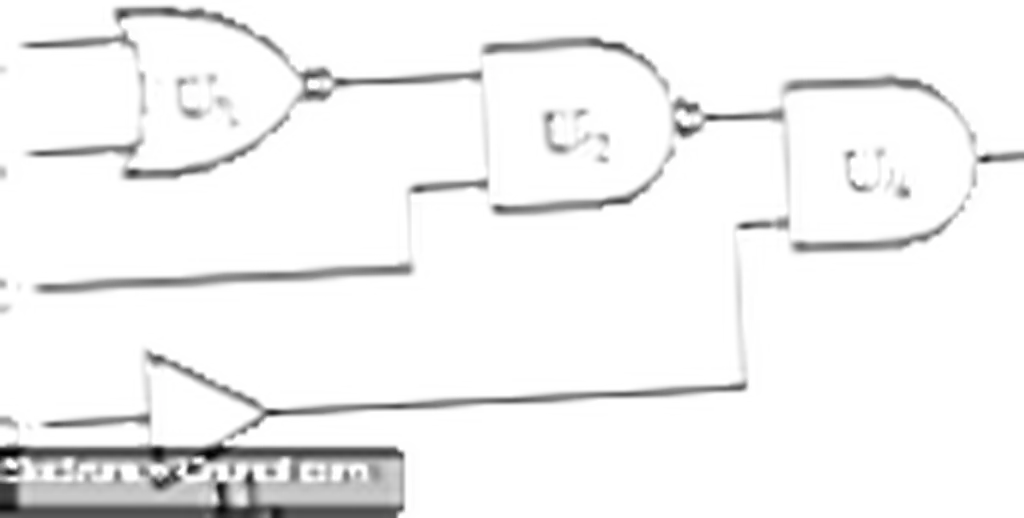

Предскажите, как будет затронута работа этой логической схемы ворот в результате следующих сбоев. Рассматривайте каждую ошибку независимо (т.е. по одному, без кратных ошибок):

|

|

- Выход логического элемента NAND U 2 не работает:

- Выход буферного затвора U 3 не работает:

- Выход NOR-ворот U 1 выходит из строя высоко:

Для каждого из этих условий объясните, почему возникнут результирующие эффекты.

Показать ответ

- Выход NAND-затвора U 2 выходит из строя низко: выход Gate U 4 застрял в низком состоянии.

- Выход буферного затвора U 3 сбой низкий: выход Gate U 4 застрял в низком состоянии.

- Выход NOR-затвора U 1 выходит из строя: выход Gate U 4 просто равен (C) D, никакие другие входы не влияют на выход U 4.

Заметки:

Цель этого вопроса заключается в том, чтобы подойти к области устранения неисправностей схемы с точки зрения понимания того, что такое ошибка, а не только знать, что такое симптомы. Хотя это не обязательно реалистичная перспектива, это помогает студентам создавать фундаментальные знания, необходимые для диагностики неисправной схемы из эмпирических данных. Такие вопросы должны сопровождаться (в конечном итоге) другими вопросами, которые задают учащимся определение вероятных ошибок на основе измерений.

Вопрос 5

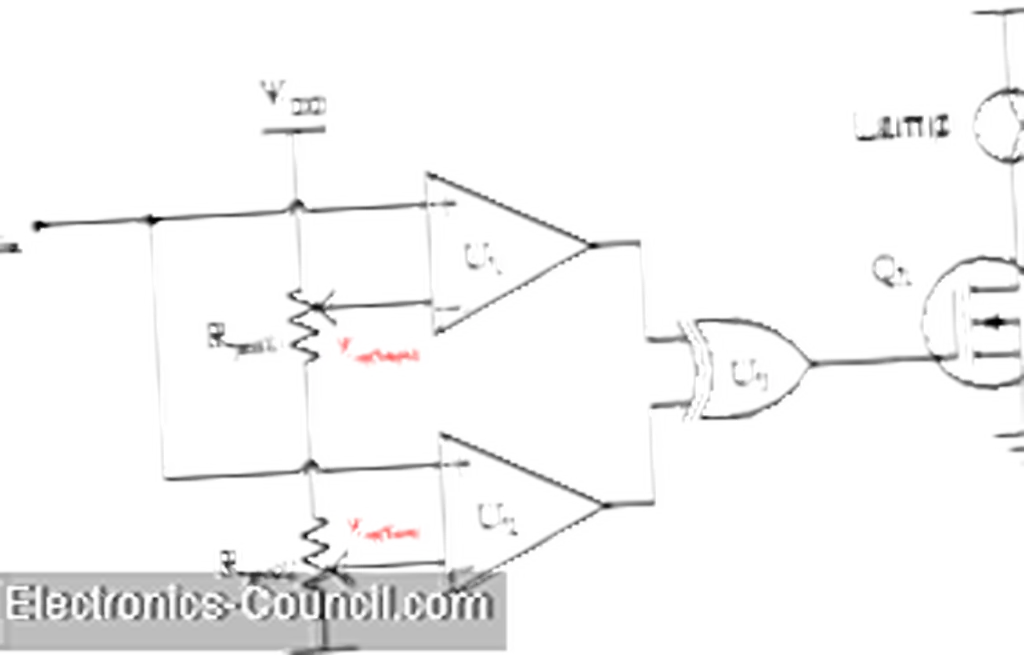

Эта схема должна возбуждать лампу, когда входное напряжение (V in) падает между двумя опорными напряжениями, установленными R pot1 и R pot2. Предскажите, как повлияет на работу этой схемы в результате следующих сбоев. Рассматривайте каждую ошибку независимо (т.е. по одному, без кратных ошибок):

|

|

- Выход компаратора U 1 сбой:

- Выход компаратора U 1 выходит из строя высоко:

- Выход компаратора U 2 не работает:

- Выход компаратора U 2 выходит из строя:

- Провод, соединяющий V DD с R pot1, не открывается:

Для каждого из этих условий объясните, почему возникнут результирующие эффекты.

Показать ответ

- Выход компаратора U 1 не срабатывает: лампа активируется, когда V в > V ref (низкий), даже если V в > V ref (высокий).

- Выход компаратора U 1 не срабатывает: лампа активируется только при V в <V ref (низкий).

- Выход компаратора U 2 не срабатывает: лампа активируется только при V в > V ref (высокий).

- Выход компаратора U 2 не срабатывает: лампа активируется, когда V в <V ref (высокий), даже если V в <V ref (низкий).

- Провод, соединяющий V DD с R pot1, не открывается: лампа отказывается активировать.

Заметки:

Цель этого вопроса заключается в том, чтобы подойти к области устранения неисправностей схемы с точки зрения понимания того, что такое ошибка, а не только знать, что такое симптомы. Хотя это не обязательно реалистичная перспектива, это помогает студентам создавать фундаментальные знания, необходимые для диагностики неисправной схемы из эмпирических данных. Такие вопросы должны сопровождаться (в конечном итоге) другими вопросами, которые задают учащимся определение вероятных ошибок на основе измерений.

Вопрос 6

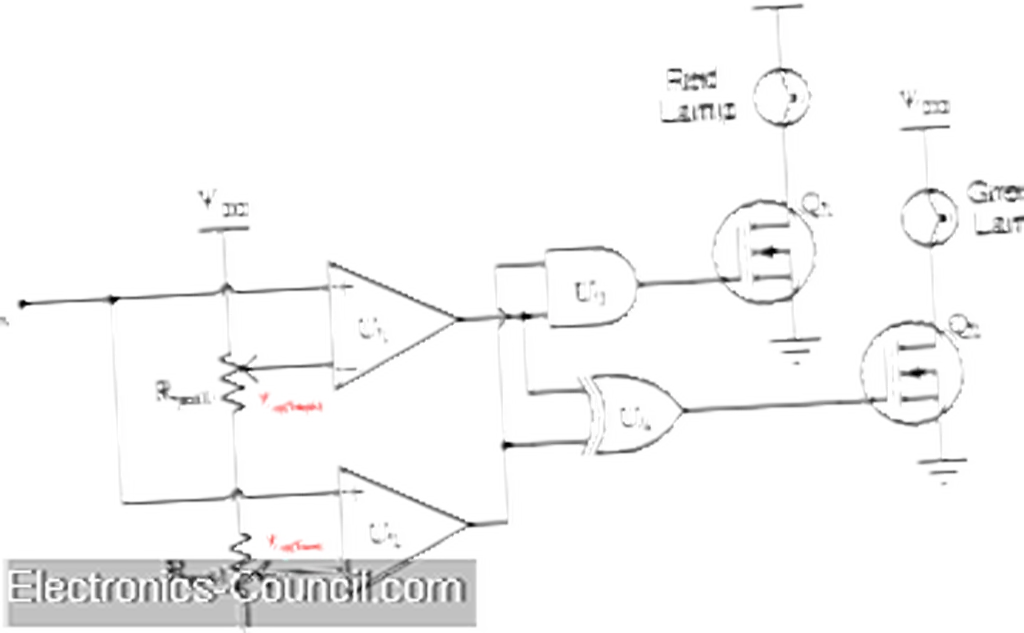

Эта схема должна возбуждать зеленую лампу, когда входное напряжение (V in) падает между двумя опорными напряжениями, установленными R pot1 и R pot2, и активирует красную лампу, когда входное напряжение превышает оба опорных напряжения. Однако в этой схеме что-то не так: зеленая лампа работает так, как должна, но красная лампа никогда не включается, даже когда она должна.

|

|

Техник решает заменить красную лампу, думая, что она сгорела. Это, к сожалению, не устраняет проблему. Определите две возможные неисправности компонентов, которые могут объяснить эту проблему, и опишите, какие дальнейшие шаги диагностики вы предпримете для определения точной природы неисправности.

Показать ответ

U 3 и Q 1 являются наиболее подозрительными компонентами, учитывая поведение схемы. Я дам вам понять, что измерить дальше!

Заметки:

Обсудите ответы своих учеников на этот вопрос и их стратегии устранения неполадок. Последняя часть вопроса, где учеников просят объяснить, что они будут делать дальше, является самой важной частью!

Вопрос 7

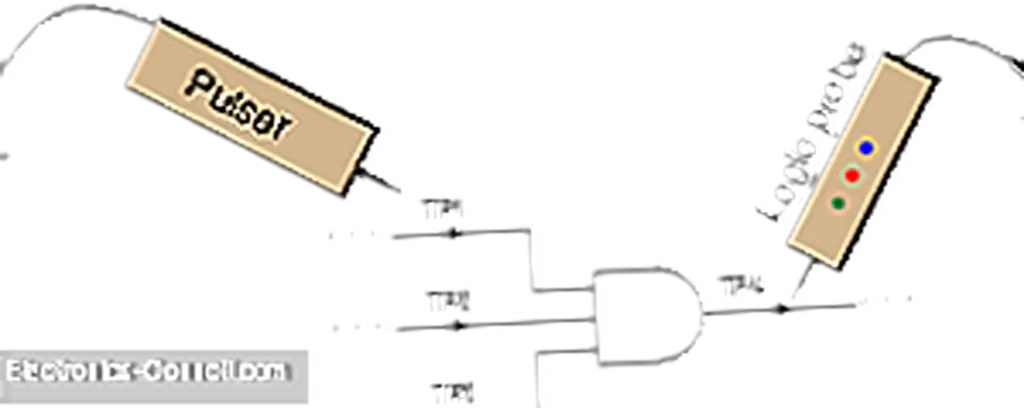

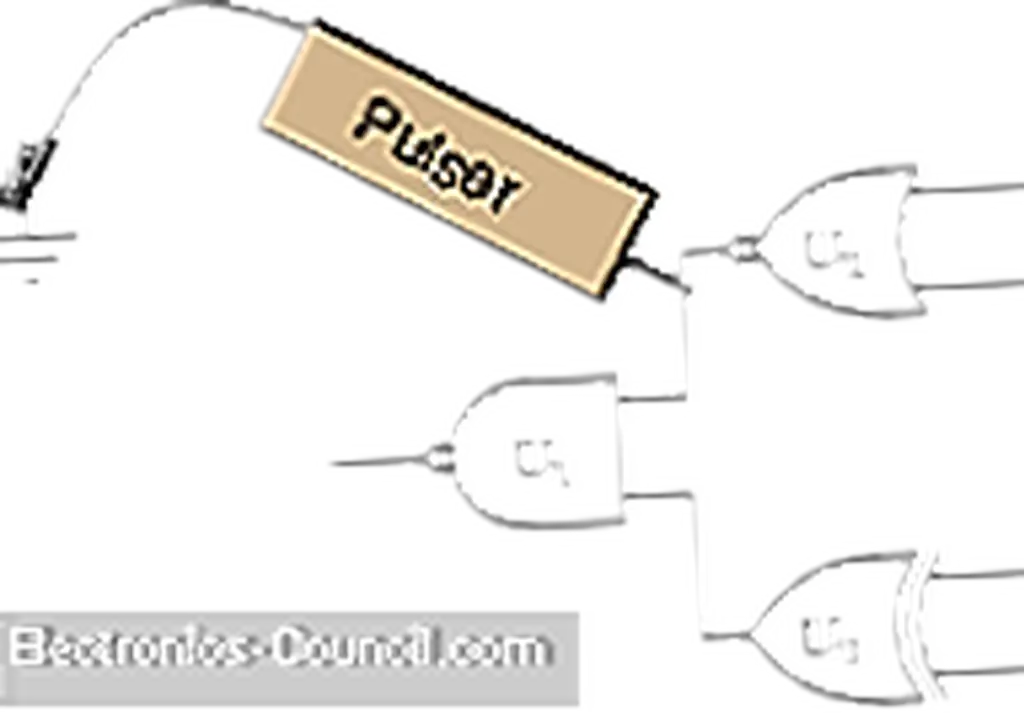

Техник решает проверить подозрительный три входа И с использованием логического пульса. Она касается логического пульсатора на каждом входе логического элемента И, и ищет импульсный сигнал на выходе с помощью логического датчика.

|

|

Независимо от того, какая контрольная точка входа (TP1, TP2 или TP3) она подает импульсы, тестовая точка вывода (TP4) всегда читается на низком уровне. Означает ли это, что логика AND неисправна? # 7 "> Показать ответ Скрыть ответ

И ворота могут быть плохими, или это может быть хорошо. Испытание, как описано, является неубедительным.

Последующий вопрос: что нужно было бы проверить, чтобы сделать описанную процедуру тестирования действительной?

Заметки:

Это очень практичный вопрос, так как он требует от студентов тщательного изучения того, что должен делать три входных логических элемента И при нормальных условиях, и как настроить тест, который действительно действителен.

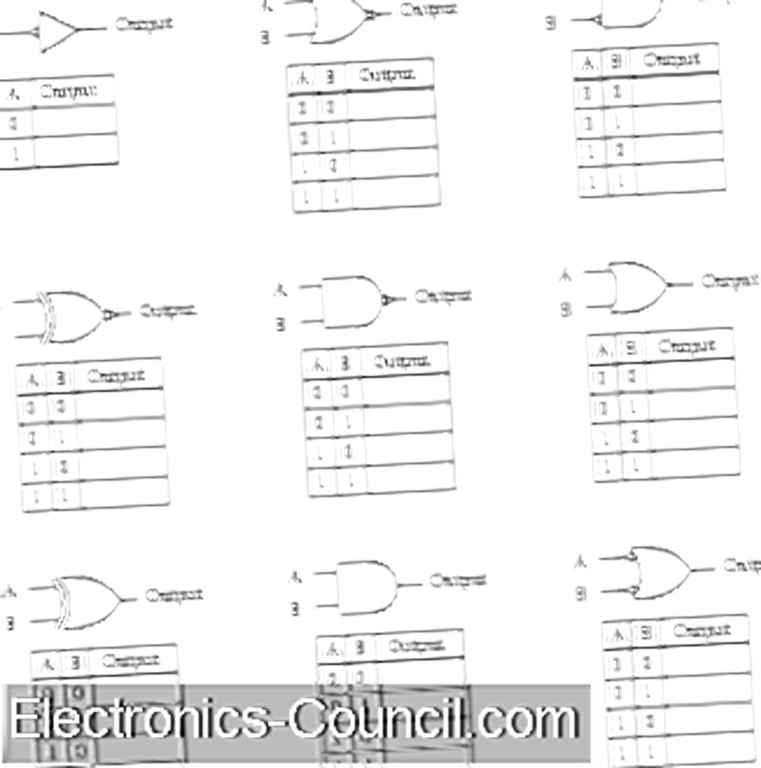

Вопрос 8

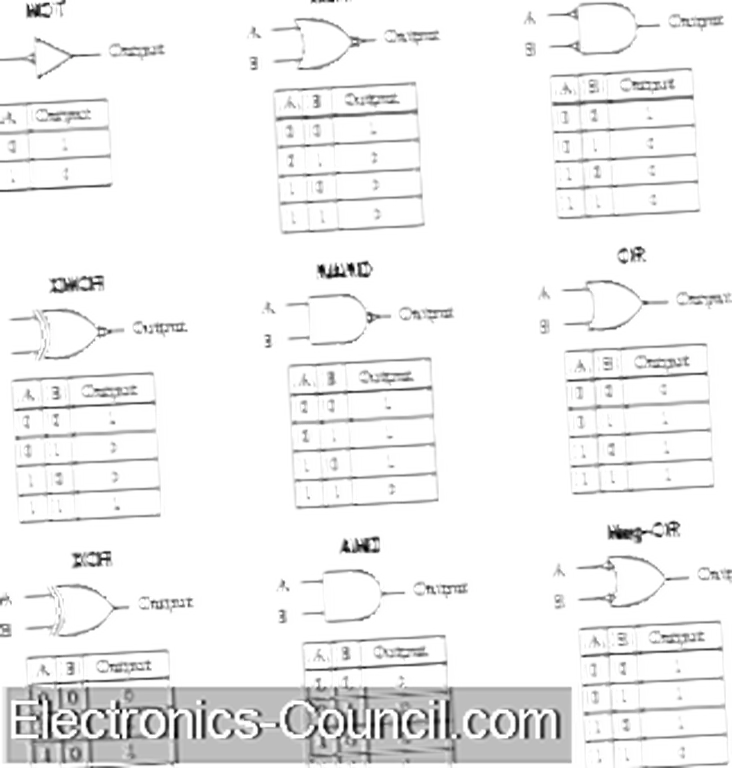

Определите каждый из этих логических ворот по имени и заполните их соответствующие таблицы истинности:

|

|

Показать ответ

|

|

Заметки:

Чтобы ознакомить студентов со стандартными типами логических ворот, мне нравится давать им практику с идентификацией и таблицами истинности каждый день. Студенты должны иметь возможность распознавать эти типы логических ворот с первого взгляда, иначе им будет сложно проанализировать схемы, которые их используют.

Вопрос 9

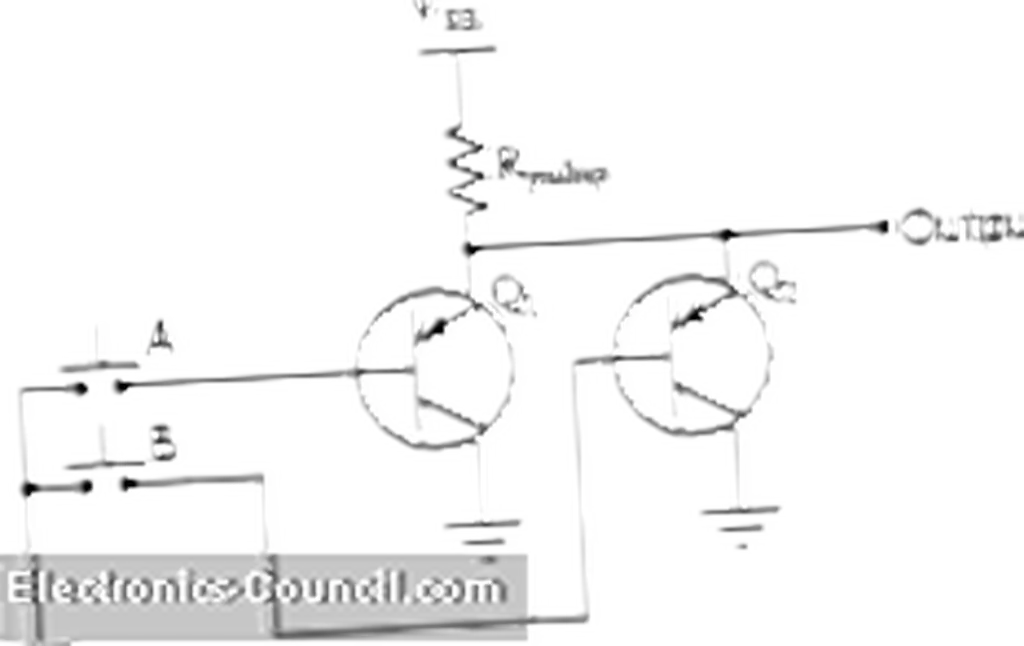

Определите по крайней мере две ошибки в этой простой логической схеме, которая может привести к сбою ее выхода в «низком» логическом состоянии:

|

|

Обязательно объясните, почему предлагаемые ошибки приведут к сбою в выходе.

Показать ответ

- Транзистор Q 1 неисправен (сборщик для эмиттера)

- Транзистор Q 2 неисправен (сборщик для эмиттера)

- Входная линия A закорочена на землю

- Входная линия B закорочена на землю

- Неисправность резистора R

Последующий вопрос: хотя все эти ошибки приведут к снижению производительности, не все из них приведут к тому, что выход будет таким же низким. Объясните это.

Заметки:

Обсудите ответы своих учеников со всеми в классе и их рассуждениями позади них.

Вопрос 10

Объясните, почему размещение статически чувствительных компонентов (например, интегральных схем CMOS) в блоке проводящей пены защищает их от повреждения от ESD и почему эта защита существует, даже если весь блок пены (с чипом) доведен до повышенного потенциала с помощью относительно земли.

Показать ответ

Проводящая пена делает контакты электрически общими друг с другом, поэтому между любыми двумя выводами компонента не может наблюдаться значительная разница напряжения.

Заметки:

Вы можете подчеркнуть этот принцип, указав своим ученикам, что вы можете подойти к куску проводящей пены с множеством вставленных в нее микросхем CMOS и прикоснуться к ней своим статическим заряженным пальцем без ущерба. Даже если вы нарисуете искру между пальцем и пеной (или любой штырь микросхемы, застрявший в пене), чипы будут защищены, потому что они не имеют напряжения между их контактами.

Вопрос 11

Для истинного TTL-затвора (не высокоскоростного CMOS), что является логическим состоянием по умолчанию для входной линии, которая остается плавающей (ни одна из них не подключена к V CC или Ground) «# 11»> Показать ответ Скрыть ответ

Плавающие входы TTL обычно предполагают «высокое» состояние из-за сети рулевого диода / резистора на входном каскаде каждой схемы затвора.

Заметки:

Данный ответ не дает достаточно подробностей, чтобы объяснить, почему входы TTL имеют тенденцию плавать высоко, поэтому я рекомендую вам отобразить внутреннюю схему TTL-ворот, чтобы ваши ученики могли анализировать и комментировать в классе.

Вопрос 12

Какое логическое состояние допускает вход плавающего входа CMOS? Как это сравнивается с традиционным TTL?

Показать ответ

Плавающий затвор CMOS не принимает никакого определенного логического состояния! Логическое состояние входа плавающего входа CMOS является неопределенным.

Последующий вопрос: какое состояние использует плавающий вход для высокоскоростного логического выхода CMOS (74HCxx), который предназначен для обновления / замены традиционных TTL-ворот?

Заметки:

Попросите ваших учеников объяснить свой ответ на основе анализа внутренних элементов CMOS-ворот, а также внутренних элементов TTL-ворот. Запоминание недостаточно хорошее - учащиеся должны понять, почему эти разные логические семьи ведут себя так же, как и они.

Вопрос 13

Как преподаватель электроники, у меня есть возможность увидеть много творческих ошибок, сделанных студентами, когда они учатся строить схемы. Одна очень распространенная ошибка в конструкции схемы CMOS проявляется в неустойчивом поведении: схема может функционировать правильно на время, но внезапно и случайным образом она останавливается. Затем, размахивая рукой рядом с контуром, он снова начинает работать!

Эта проблема особенно распространена в дни, когда влажность воздуха низкая, а статические электрические заряды легко накапливаются на объектах и людях. Объясните, какая ошибка проводки CMOS привела к тому, что логический вентиль с питанием будет вести себя непредсказуемо из-за соседних статических электрических полей и каково надлежащее решение этой проблемы.

Показать ответ

Эта классическая проблема вызвана отсутствием подтягивающих или выпадающих резисторов на входах CMOS-затвора.

Заметки:

Студенты считают, что я волшебник, способный устранить неисправность их схем CMOS, просто махая рукой рядом с ними. Нет, я просто мудрый по пути общей ошибки студента!

Вопрос 14

Объясните, почему допустимый диапазон напряжения питания для истинного TTL (не высокоскоростного CMOS) логического затвора настолько узкий. Каков типичный диапазон напряжений питания для истинного TTL-затвора и почему этот тип логических вентилей не может работать из более широкого диапазона напряжений, поскольку CMOS-ворота могут?

Показать ответ

Из-за требований к смещению своих составляющих биполярных транзисторов схема TTL требует гораздо более тесного напряжения питания, чем CMOS. Я расскажу вам, что это за типичный диапазон!

Заметки:

Многие из старых логических схем 74xx и 74LSxx считаются устаревшими, но их все еще можно найти во многих операционных устройствах! Это не редкость, когда студенты ошибочно изучают данные нового семейства логики, такие как 74HCxx, которые имеют разные требования к источнику питания, чем традиционные TTL. Будьте готовы подробно рассказать о различиях между этими семействами IC, если и когда ваши ученики столкнутся с этой путаницей!

Вопрос 15

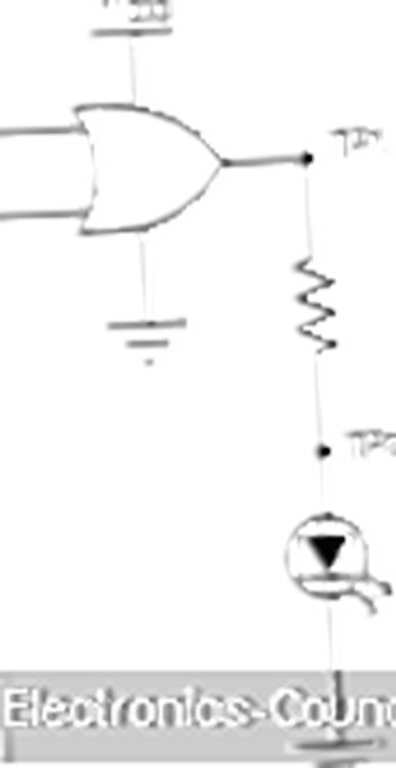

Логические зонды являются полезными инструментами для устранения неисправностей схем цифровых логических логических схем, но они, безусловно, имеют ограничения. Например, в этой простой схеме логический зонд будет давать правильные «высокие» и «низкие» показания в тестовой точке 1 (TP1), но он всегда будет читать «низкий» (даже если светодиод включен) в контрольной точке 2 (ТР2):

|

|

Теперь, очевидно, выход затвора «высок», когда светодиод горит, иначе он не получит достаточное напряжение для подсветки. Почему тогда логический зонд не может указать высокое логическое состояние на TP2 «# 15»> Показать ответ Скрыть ответ

Я не буду давать ответ здесь, но он имеет какое-то отношение к правильному напряжению на уровне логики CMOS.

Последующий вопрос: эта светодиодная схема довольно проста, и сценарий почти глупый, потому что присутствие светодиода делает проверку логического состояния на TP1 и TP2 излишним! Можете ли вы придумать какую-либо другую схему или ситуацию, когда подобное ложное считывание может отображаться логическим зондом - где логическое состояние не было визуально очевидным благодаря наличию светодиода?

Заметки:

Студенты легко упускают из виду ограничения логического зонда и забывают, что на самом деле заставляет его говорить «высокий» или «низкий» при измерении логического уровня. Вот почему в низкоскоростных схемах я предпочитаю использовать хороший цифровой вольтметр, а не логический зонд, чтобы различать логические состояния. С помощью вольтметра вы можете точно видеть, что такое уровень напряжения, и определить, является ли логическое состояние маргинальным.

Вопрос 16

Полезным инструментом для диагностики неисправностей цифровой схемы ворот является логический импульс. Объясните, что это такое, и дайте пример того, как он используется.

Показать ответ

Поскольку большинство электронных учебников по электронике обсуждают логический пульсатор вместе с логическими пробниками, я позволю вам провести исследование здесь и поделиться со своими одноклассниками и инструктором, что вы нашли!

Заметки:

Студенты могут задаться вопросом, как логический импульс способен переопределить состояние вывода любых подключенных к нему ворот. Ответ связан с кратковременным временем работы пульсатора, а также с низким импедансом пульсатора (по сравнению с относительно высоким импедансом выхода завышенных ворот).

Вопрос 17

Техник использует логический импульс для принудительного логического состояния провода, соединяющего два из ворот:

|

|

Какие ворота или ворота проверяем, помещая пульсатор в это положение «# 17»> Показать ответ Скрыть ответ

В этом месте, пульс установлен для проверки затвора U 1. Для завершения теста нам понадобится использовать логический зонд с возможностью индикации «импульс» на выходе U 1.

Импульс требует заземления, поэтому он может подавать ток в или из тестируемой цепи. Без заземления не было бы полного пути для тока, и пульсатор не смог бы «переопределить» выходное состояние затвора NOR.

Последующий вопрос: какое логическое состояние должен использовать другой вход вентилятора NAND для этого теста? Объяснить, почему.

Заметки:

То, что я пытаюсь передать с этим вопросом, заключается в том, что принудительное выключение выхода с высоким или низким уровнем с помощью логического пульсатора ничего не говорит об этих воротах. Мы используем пульсатор для перекрытия выходов затвора, чтобы проверить функцию ворот, принимающих этот сигнал. Другими словами, мы используем пульсатор для проверки затворов «ниже по течению», где пульсатор контактирует с контуром.

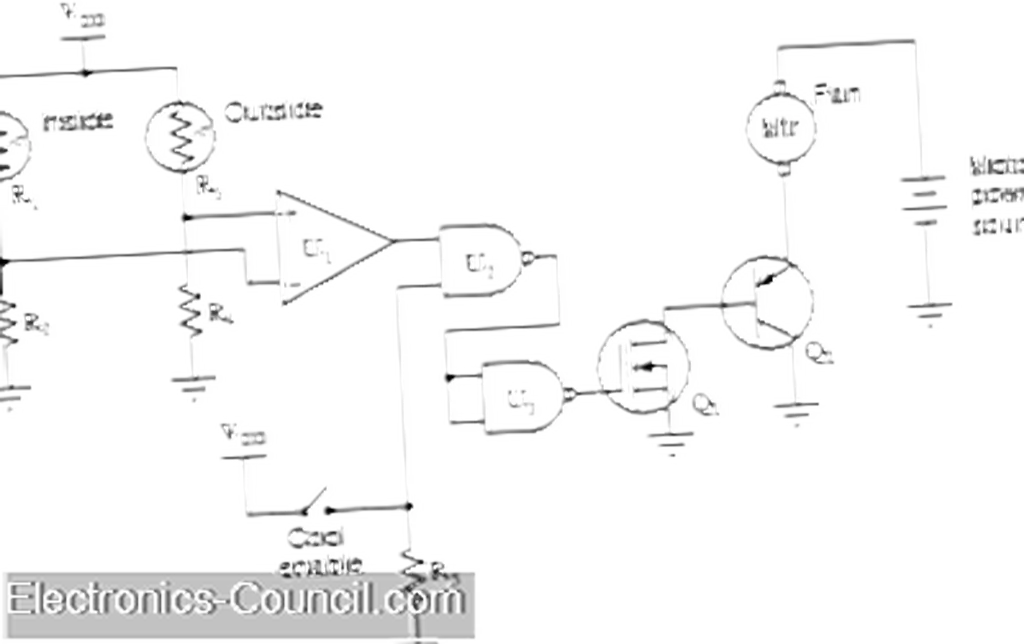

Вопрос 18

В этой схеме устанавливается компаратор, чтобы определить, больше ли внешняя или внутренняя температура, и включает вентилятор охлаждения, когда условия правильные. Предскажите, как повлияет на работу этой схемы в результате следующих сбоев. Рассматривайте каждую ошибку независимо (т.е. по одному, без кратных ошибок):

|

|

- Выход компаратора U 1 сбой:

- Выход NAND-ворот U 2 выходит из строя низко:

- Выход NAND-ворот U 2 выходит из строя высоко:

- Транзистор Q 1 не замыкается (сбрасывается в источник):

- Резистор R 2 не работает:

- Термистор R 3 не работает:

- Резистор R 4 не работает:

- Паяный мост (короткий) через термистор R 1:

Показать ответ

- Выход компаратора U 1 не работает: вентилятор никогда не включается.

- Выход NAND-ворот U 2 выходит из строя низко: вентилятор всегда остается включенным.

- Выход NAND-ворот U 2 выходит из строя высоко: вентилятор никогда не включается.

- Транзистор Q 1 не замыкается (сбрасывается в источник): вентилятор всегда остается включенным.

- Резистор R 2 не работает: вентилятор не включается.

- Термистор R 3 не работает: вентилятор не включается.

- Резистор R 4 не работает: вентилятор всегда остается включенным.

- Паяный мост (короткий) через термистор R 1: вентилятор не включается.

Последующий вопрос: действительно ли Q 1 источник или приемник теряет «заметки скрыты»> Примечания:

Такие вопросы помогают студентам оттачивать свои навыки устранения неполадок, заставляя их анализировать последствия каждой возможности. Это важный шаг в устранении неполадок и требует четкого понимания функции схемы.

Вопрос 19

Выходной сигнал следующей схемы затвора всегда низкий, независимо от того, в каком состоянии находятся входные переключатели. Предположим, что здесь используются логические логики CMOS:

|

|

Определите, какая из этих возможностей может объяснить, что выход всегда низкий:

- Выход U 1 застрял в высоком состоянии

- Выход U 1 застрял в низком состоянии

- R 1 не удалось открыть

- Выключен сбой C

- Выключен переключатель B

- Переключатель A не замкнут

Показать ответ

Только эти две возможности могут объяснять, что выход всегда низкий:

- Выход U 1 застрял в низком состоянии

- Выключен сбой C

Последующий вопрос: определите, что будет делать каждая из других ошибок в цепи.

Заметки:

Такие вопросы помогают студентам оттачивать свои навыки устранения неполадок, заставляя их анализировать последствия каждой возможности. Это важный шаг в устранении неполадок и требует четкого понимания функции схемы.

Если студент предполагает, что отказ коммутатора B с открытым доступом может привести к тому, что выход остается низким, они либо неправильно понимают работу логического элемента ИЛИ, либо предполагают, что переключатель A также не работает (или что-то еще происходит, что ведет к задержке ввода)). Я часто нахожу такое предположение у студентов, новых для устранения неполадок: допуская множественные ошибки. Хотя множественные ошибки не являются невозможными, они менее вероятны, чем одиночные ошибки. Поэтому хороший техник сначала ищет отдельные ошибки, способные учитывать все наблюдаемые состояния перед поиском (менее вероятными) комбинаций неисправностей. Это практическое применение бритвы Оккама.

Вопрос 20

Выходной сигнал следующей схемы затвора всегда высок, независимо от того, в каком состоянии находятся входные переключатели. Предположим, что здесь используются логические устройства CMOS:

|

|

Определите, какая из этих возможностей может объяснить выход всегда высоким:

- Выход U 1 застрял в высоком состоянии

- Выход U 2 застрял в высоком состоянии

- R 1 не удалось открыть

- R 2 не замкнут

- R 3 не удалось закрыть

- Переключатель A не работает

- Переключатель B не замкнут

- Сбой выключателя C

Показать ответ

Только эти три возможности могут объяснять, что выход всегда высок:

- R 1 не удалось открыть

- R 3 не удалось закрыть

- Переключатель B не замкнут

Заметки:

Такие вопросы помогают студентам оттачивать свои навыки устранения неполадок, заставляя их анализировать последствия каждой возможности. Это важный шаг в устранении неполадок и требует четкого понимания функции схемы.

Вопрос 21

Следующая схема ворот имеет проблему:

|

|

При тестировании обнаруживается, что схема не отвечает так же, как предсказывает ее (идеальная) таблица истинности. Вот сравнение идеальных и фактических таблиц истинности, как прогнозировалось и проверено:

-

В С Выход (идеальный) Выход (фактический) 0 0 0 1 1 0 0 1 0 0 0 1 0 1 1 0 1 1 1 0 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1

Разумеется, первое, что должен сделать хороший техник-электроник, - это либо вольтметр, либо логический зонд, и начать тестирование логических уровней в цепи, чтобы понять, что не так. Однако настройки входных переключателей очень важны как часть диагноза. На основе схемы схемы и показанных результатов таблицы истинности, в каких состояниях (открытых или закрытых) вы бы сначала установили входные переключатели, а затем какой логический уровень вы бы сначала протестировали с помощью логического датчика или вольтметра «# 21», > Показать ответ Скрыть ответ

Настройки переключателя:

- Открытое (0)

- B закрыто (1)

- C закрытый (1)

Затем измерьте логическое состояние нижнего входа на вентиле NOR (исходящего из переключателя «B»).

Заметки:

Попросите ваших учеников объяснить, какое логическое состояние должно быть в этой точке цепи, и какое логическое состояние они подозревают, возможно, что это может объяснить аберрантный вывод. Также обсудите, почему этот конкретный выбор настроек коммутатора является лучшим для первого теста.

Если ученики не сразу поймут, почему переключатели должны быть установлены, как указывает ответ, создайте следующий сценарий. Предположим, что их попросили устранить простую схему лампочек, используя только вольтметр. Проблема в том, что лампочка не загорается, когда переключатель закрыт. Было бы лучше продолжить измерения напряжения при включении или выключении переключателя? Должно быть легко понять, что включение переключателя в выключенном положении только помешает диагнозу, и что включение выключателя - лучший способ выявить неисправность (чтобы можно было использовать вольтметр, чтобы увидеть, где нет напряжения, но должно быть). Аналогичным образом, разумно настроить эту неисправную логическую схему таким образом, что выход должен делать что-то не так. Таким образом, можно легко сравнивать логические состояния, как они есть, так как они должны быть, и оттуда определить, какой тип ошибки может вызвать проблему.

Вопрос 22

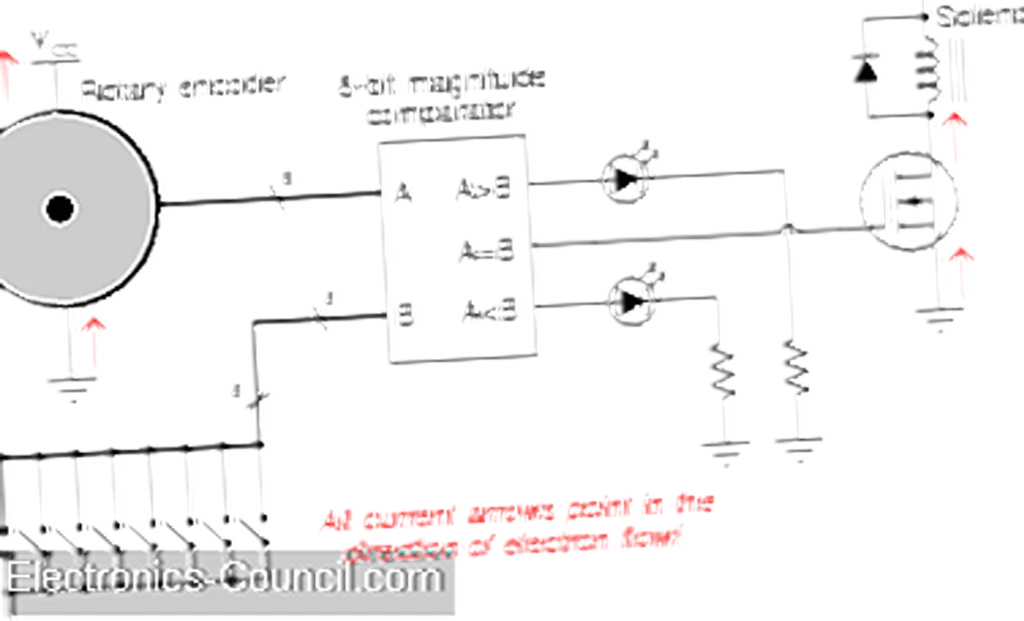

Целью этой схемы является указание того, когда вал вращающегося датчика находится в определенном положении (соответствующем настройке 8-позиционного переключателя):

|

|

Проследите направления всех токов в этой цепи, используя нотацию электронного потока, когда положение датчика соответствует предварительно установленному коду, введенному на переключателях. Затем определите отказы отдельных компонентов, которые могут привести к тому, что катушка соленоида не активируется в этом состоянии.

Показать ответ

|

|

Потенциальные неисправности компонентов, приводящие к неактивации соленоида:

- MOSFET не удалось открыть (утечка в источник)

- Сломанная проволока между дросселем MOSFET и катушкой соленоида

- Потеря мощности (V CC) в схему компаратора

- Потеря мощности для кодировщика (только если код коммутатора не 0000 0000)

Заметки:

Обсудите варианты ошибок со своими учениками, попросив их объяснить, почему каждая предлагаемая ошибка приведет к тому, что соленоид не активируется.

- ← Предыдущая работа

- Индекс рабочих листов

- Следующая рабочая таблица →