Умножение частоты PLL: переходный ответ и синхронный синтез

Является ли добавление делителя обратной связи влияющим на фазовый цикл (ФАПЧ) переходным ответом? Мы рассмотрим этот вопрос и другие темы частотного умножения в этой статье.

Вспомогательная информация

- Что точно представляет собой фазовую петлю, в любом случае?

- Как имитировать цикл с фазовой блокировкой

- Понимание переходных процессов с фазовой синхронизацией

- Как оптимизировать переходный отклик цикла с фазовой блокировкой

- Проектирование и имитация оптимизированного цикла с фазовой блокировкой

- Понимание приложений PLL: умножение частоты

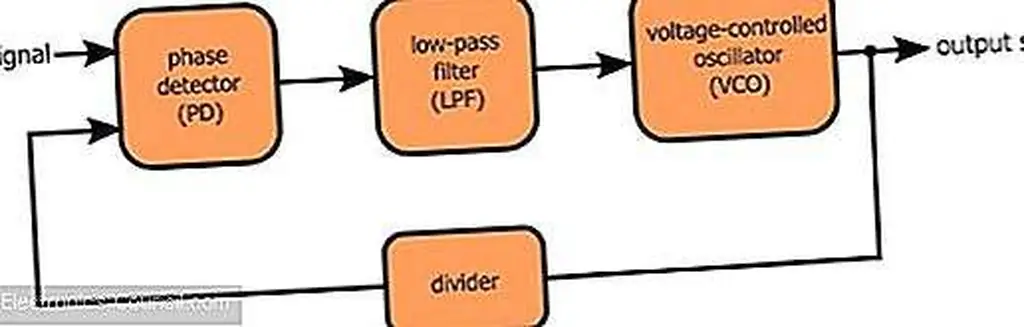

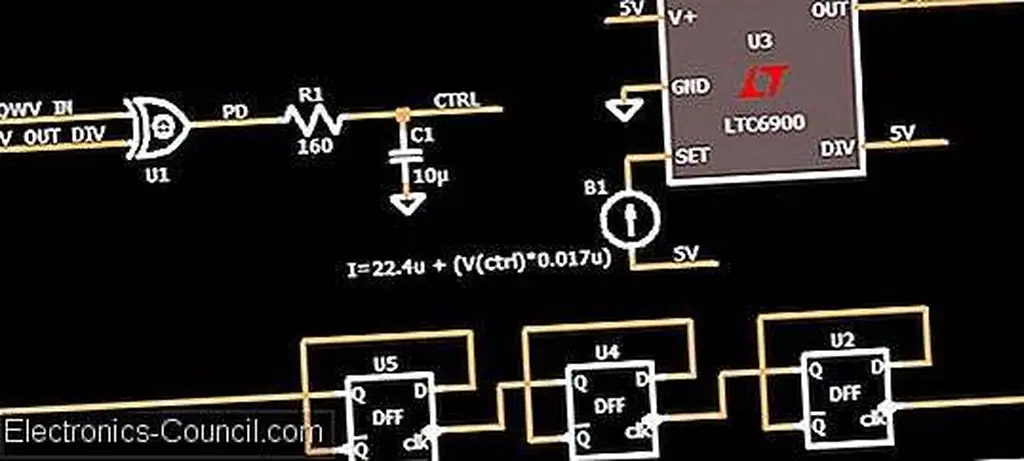

В предыдущей статье о умножении частоты, мы убедились, что петля фазовой автоподстройки может производить выходной сигнал с частотой, которая выше, чем частота входного сигнала (АКА в качестве ссылки). Это достигается за счет включения делителя в контур обратной связи.

Этот высокочастотный сигнал «наследует» желаемые характеристики (т. Е. Точность частоты и стабильность во времени и температуре) от входного сигнала. Следовательно, низкокачественный управляемый напряжением генератор в сочетании с высококачественным (но низкочастотным) опорным сигналом может генерировать высококачественную высокочастотную волну.

Назад к переходному отклику

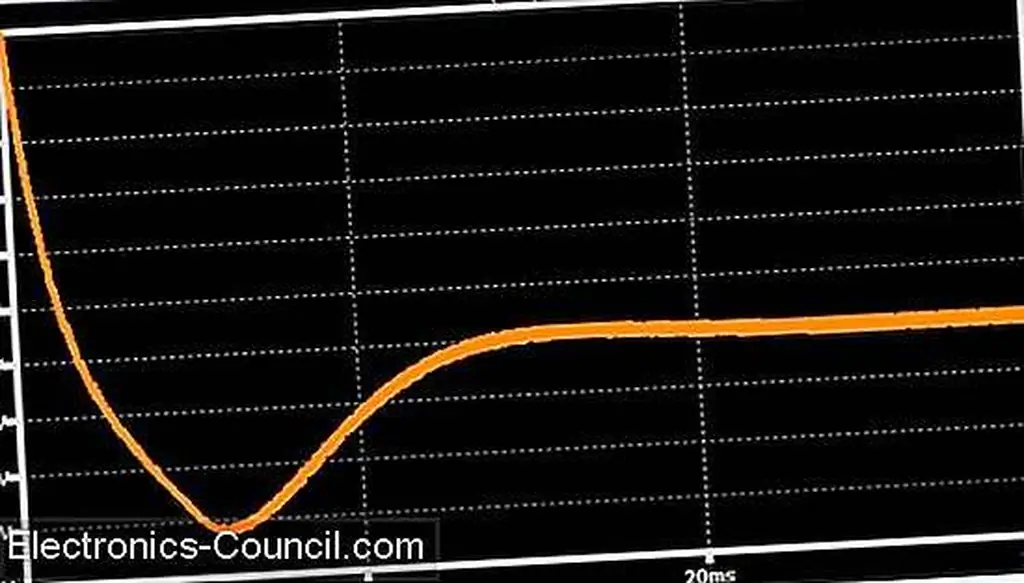

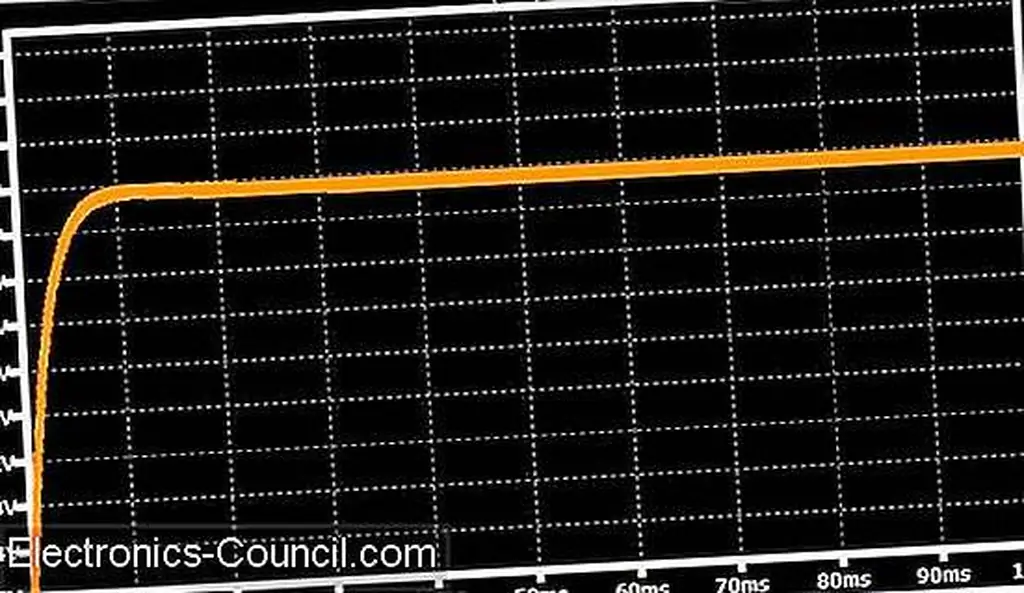

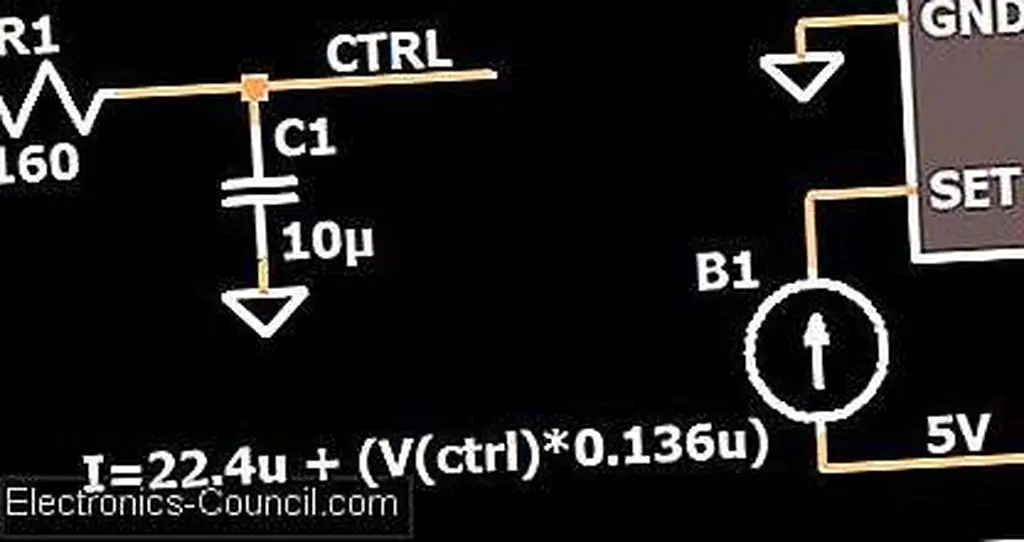

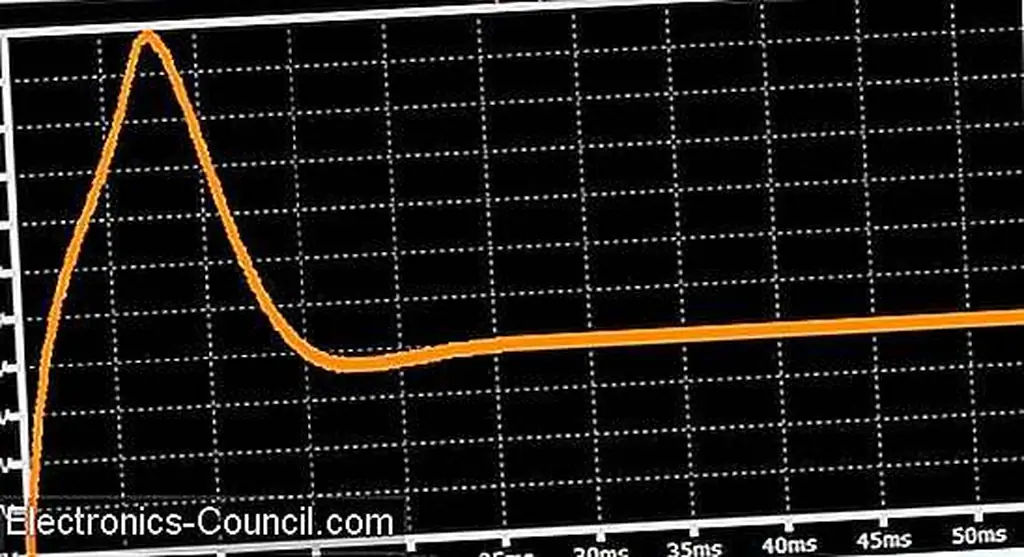

Мы уже обсуждали переходный ответ PLL и, более конкретно, как создать PLL с желательным коэффициентом демпфирования. Следующий график дает вам пример управляющего напряжения PLL, который быстро и плавно устанавливается на конечное значение:

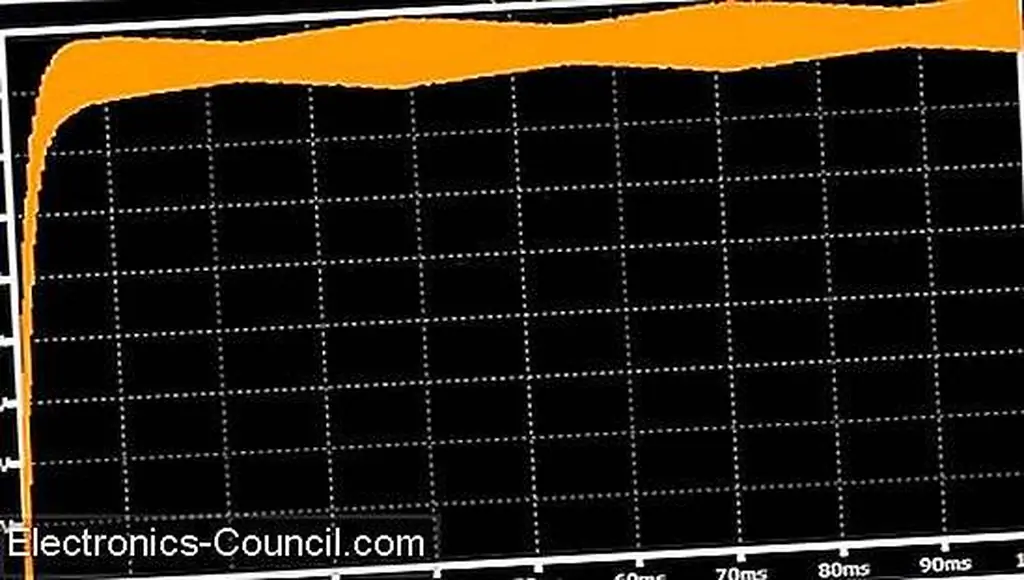

Следующий график показывает управляющее напряжение для той же самой схемы, за исключением того, что я добавил счетчик «разделить на два» в контур обратной связи.

Это не выглядит ужасно, но что-то определенно изменилось. Кроме того, управляющее напряжение не достигает стабильного состояния - вы можете видеть периодические изменения амплитуды пульсаций.

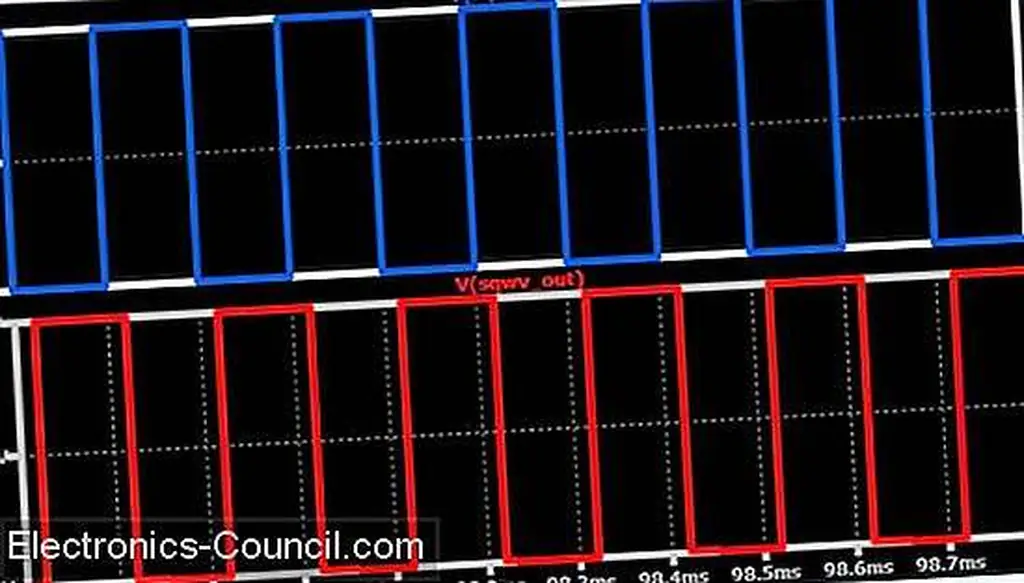

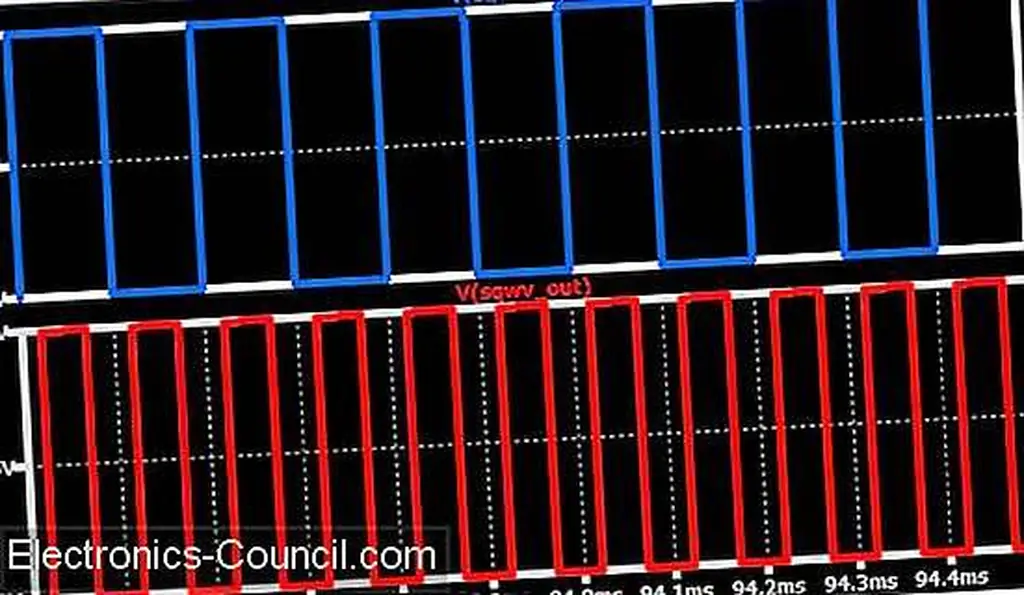

Если мы увеличим масштаб и посмотрим на входные и выходные сигналы, ясно, что у нас есть более серьезная проблема:

Выходная частота (f OUT) определенно не в два раза превышает входную частоту (f IN). Проблема здесь в том, что начальный управляющий ток VCO не достаточно близко к 2f IN; другими словами, невозможно, чтобы управляющее напряжение отрегулировало частоту VCO до 2f IN.

Итак, первое, что нам нужно сделать, это удвоить смещение текущего источника; это приведет к тому, что ток начального управления достигнет значения, которое создает f OUT, который находится вблизи f IN.

Как показывают следующие два графика, PLL работает довольно хорошо. Переходный ответ проявляет хорошее демпфирование и f OUT = 2f IN.

Частота умножения, умножение усиления

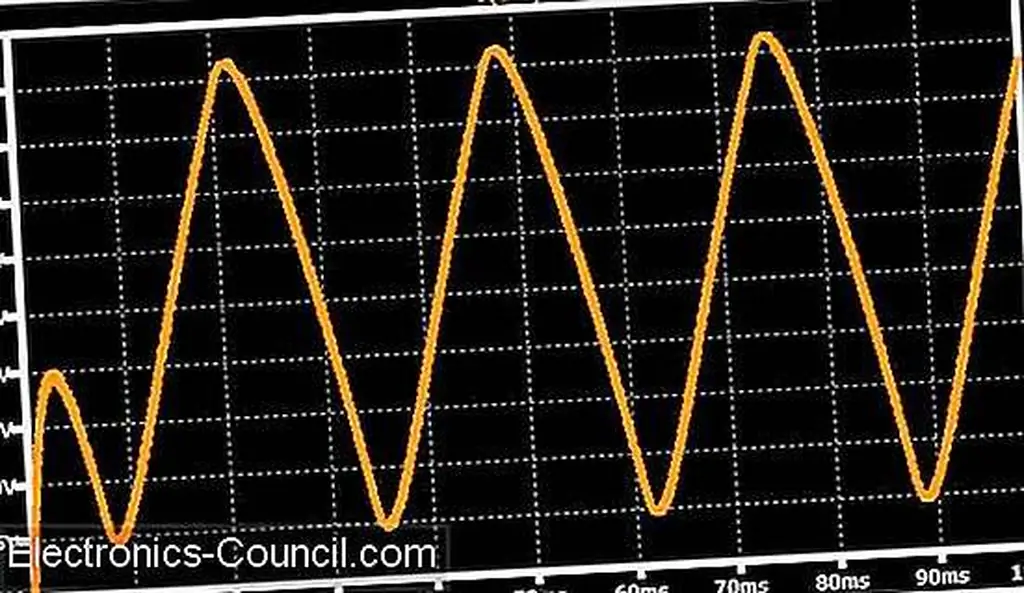

К сожалению, этот последний набор симуляций нас обманул. PLL работает хорошо, да, но это только потому, что коэффициент умножения (обозначается N) настолько низок. Когда N = 2, переходный отклик все еще неплох, но если мы добавим больше счетчиков на два, так что N = 8, будет обнаружена скрытая проблема:

Это определенно не то, что я бы назвал критически затухающим переходным ответом. На самом деле, похоже, что PLL никогда не достигнет блокировки. Это действительно неудивительно, хотя, если мы сделаем шаг назад и подумаем о влиянии делителя. Из предыдущих статей известно, что на коэффициент демпфирования влияет K, который я описал как общий коэффициент усиления системы, т. Е. Коэффициент усиления фазового детектора, умноженный на коэффициент усиления VCO. Но более точное описание K является «петлевым» усилением, и путь обратной связи, конечно, является частью цикла.

В базовом PLL путь обратной связи не влияет на K, потому что это просто прямая связь; таким образом, K = K PD × K VCO. Но теперь у нас есть разделитель в пути обратной связи, так что общий коэффициент усиления становится

$$ K = \ frac {K_ {PD} times K_ {VCO}} {N} $$

Суть в том, что мы больше не имеем хорошего коэффициента демпфирования, потому что коэффициент усиления контура изменился. К счастью, средство просто: мы умножаем коэффициент усиления VCO (или PD) на N, чтобы компенсировать деление на N. Как вы можете видеть на новом графике управляющего напряжения, желаемый переходный ответ был восстановлен.

Частотная гибкость

На этом этапе мы хорошо знаем, как умножать входную частоту с использованием PLL и как модифицировать схему так, чтобы частота «усиления» не испортила наш переходный отклик. Однако в настоящее время функциональность системы несколько ограничена.

Предположим, мы потратили хорошие деньги на очень качественный генератор на базе кристалла 1 МГц, а затем пошли на проблему разработки сказочной PLL, чтобы мы могли генерировать множество частот из этих эталонных часов. Однако, только с разделителем в пути обратной связи, частотные опции весьма ограничены: 2 МГц, 3 МГц, 4 МГц и т. Д. И, фактически, если мы реализуем разделение с каскадным разделителем на два триггера, мы 'ограничено 2 МГц, 4 МГц, 8 МГц и т. д.

Это может быть приемлемым в некоторых приложениях, но если вы хотите больше гибкости, вы можете включить делитель перед фазовым детектором:

Теперь у нас есть N INPUT и N FEEDBACK. Входная частота PLL становится f REFERENCE / N INPUT, а затем эта частота умножается на N FEEDBACK. Таким образом, $$ f_ {OUT} = \ frac {f_ {REFERENCE}} {N_ {INPUT}} times N_ {FEEDBACK} = f_ {REFERENCE} times \ frac {N_ {FEEDBACK}} {N_ {INPUT}} $$

Как вы можете видеть, теперь у нас есть возможность умножить опорную частоту на фракции вместо целых.

Возможно, вы слышали термин «дробный-N PLL», и было бы вполне понятно, если бы вы предполагали, что это относится к архитектуре с разделителем-умножением, показанной выше. Однако это не так. Фракл-N PLL основаны на более сложном методе, в котором значение делителя изменяется между N и N + 1 таким образом, чтобы создать среднее значение делителя, равное N плюс дробь. Этот процесс приводит к нежелательной модуляции частоты VCO, но отрицательные эффекты этой модуляции могут быть смягчены путем рандомизации и формирования шума.

Вывод

Мы обсудили влияние частотного «усиления» на переходный отклик PLL, и мы увидели, что надлежащий коэффициент демпфирования можно восстановить, увеличив коэффициент усиления VCO. Что касается синтеза частот, то теперь мы знаем, что разделитель (помещенный перед фазовым детектором) может расширить наши опции умножения частоты. Мы закончили с кратким объяснением архитектуры дробного N. Возможно, в дальнейшем мы рассмотрим более подробно PLL-модули с фракцией-N; честно говоря, хотя я могу быть сожжен в статьях PLL к тому времени, когда я готов заняться этой темой.

Если вы хотите самостоятельно провести эксперименты с PLL, не стесняйтесь немного сэкономить время, загрузив мою схему LTspice (просто нажмите оранжевую кнопку).

Схема LTspice