Целое и его подтипы в VHDL

В этой статье мы обсудим тип данных VHDL integer.

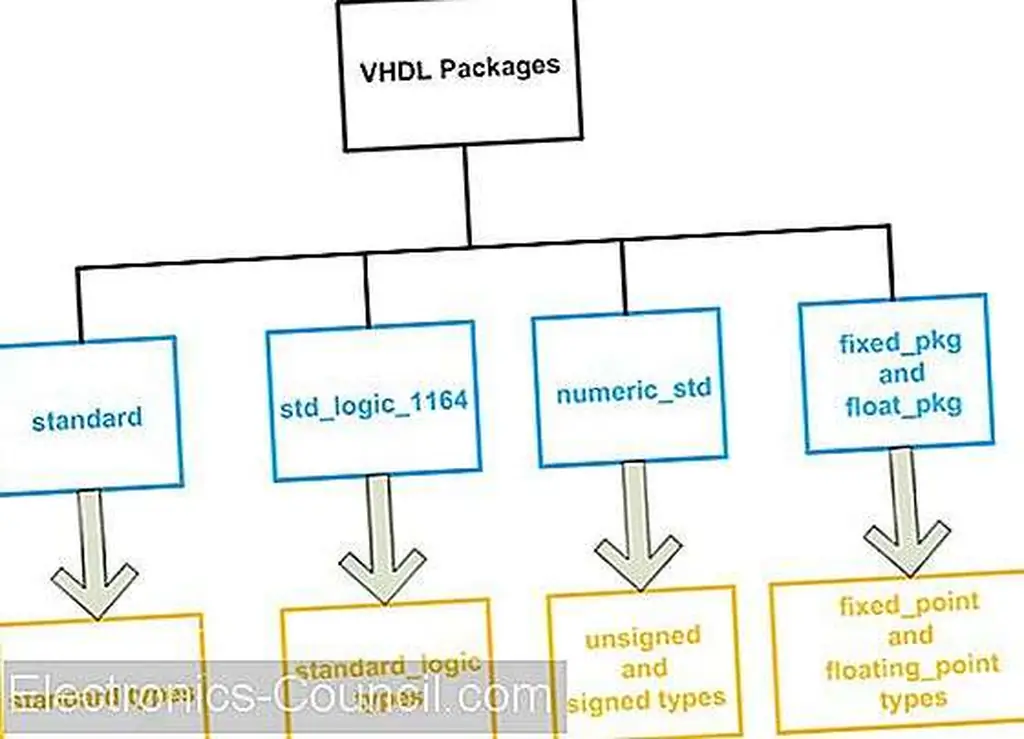

VHDL предоставляет нам несколько опций для типа данных объектов. Мы уже рассмотрели std_logic, std_logic_vector и перечисленные типы, а в предыдущей статье обсуждалась классификация типов данных на основе пакета, который определяет тип. В этой статье будет продолжено обсуждение типа данных, основное внимание будет уделено целочисленному типу данных.

Классификация типов данных VHDL

В предыдущей статье мы классифицировали типы данных VHDL на основе пакета, который дает определение типа. Это показано на рисунке 1.

Рисунок 1. Пакеты VHDL (показаны синим цветом) и типы данных, определенные в каждой упаковке (показаны оранжевым цветом)

Мы также подробно рассказали о «стандартных типах» из «стандартного» пакета. В этой статье обсуждается целочисленный тип данных и его подтипы.

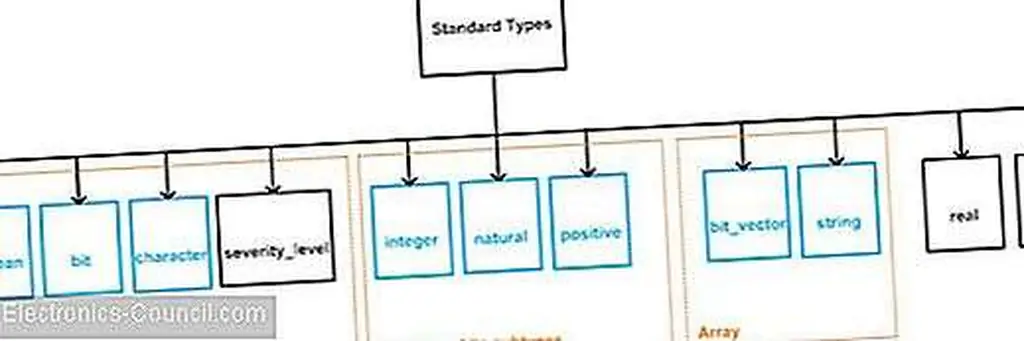

Рисунок 2. Тип данных «целочисленный» и его подтипы определены в «стандартном» пакете

Тип данных Integer

Мы можем использовать целочисленный тип данных для определения объектов, значение которых может быть целым числом. Например, следующие строки определяют сигнал sig_int типа integer и присваивают ему целое число 4.

signal sig_int: integer; sig_int <= 4;

Как показано на рисунке 2, целочисленный тип данных относится к категории «стандартные типы», который определен в «стандартном» пакете из библиотеки «std». Как обсуждалось в предыдущей статье, нам не нужно явно отображать «стандартный» пакет и библиотеку «std» для дизайна.

Следующий код показывает простой пример, когда два входа типа integer, in1 и in2, складываются вместе, и результат присваивается out1.

1 library IEEE; 2 entity IntegerTest1 is 3 port(in1, in2: in integer; 4 out1: out integer); 5 end IntegerTest1; 6 architecture Behavioral of IntegerTest1 is 7 begin 8 out1 <= in1 +in2; 9 end Behavioral;

На рисунке 3 показано симуляция ISE приведенного выше кода. На этом рисунке показан десятичный эквивалент значений ввода / вывода. Например, от 200 нс до 300 нс, входы in1 и in2 равны 3 и -1 соответственно. Таким образом, выход, out1, равен 3 + (- 1) = 2.

Рисунок 3

При использовании целочисленного типа данных мы не принимаем непосредственного участия в определениях уровня бит; однако ясно, что реализация будет использовать несколько бит для представления определенных сигналов. Сколько битов будет использоваться для представления целочисленных сигналов в приведенном выше коде «hljs»> 1 библиотека IEEE; 2 entity IntegerTest1 - это 3 порта (in1: целочисленный диапазон от 0 до 45; in2: в целых числах от -45 до 45; 4 out1: out целочисленный диапазон от -45 до 90); 5 end IntegerTest1; 6. Поведение IntegerTest1 - это 7 begin 8 out1 <= in1 + in2; 9 конец Поведенческий;

Этот код предполагает, что входы in1 и in2 находятся в диапазонах от 0 до 45 и от -45 до 45 соответственно. Поскольку out1 равно in1 + in2, диапазон out1 будет от -45 до 90. Ограничение диапазона целых чисел уменьшает объем ресурсов FPGA, необходимых для реализации дизайна. Более того, это дает нам возможность проверить ошибки на ранних этапах проектирования. Например, предположим, что out1 представляет собой угол, и из системных спецификаций мы знаем, что значение этого угла ограничено диапазоном от -45 до 90.

Как указано в приведенном выше коде, мы можем применить этот диапазон к определению объекта out1. Теперь, если мы допустим ошибку, которая заставляет значение out1 находиться за пределами указанного диапазона, программное обеспечение симулятора выдает ошибку и идентифицирует строку кода, которая включает недопустимое присвоение. Например, если мы укажем диапазон out1 как -45 до 89, а затем назначим значение 45 как в 1, так и в2, симулятор ISIM прекратит моделирование со следующей ошибкой (ISim - это имя симулятора, включенного в ISE):

ОШИБКА: В процессе IntegerTest1.vhd: 17

значение 90 находится вне допустимого диапазона от -45 до 89

INFO: Симулятор остановлен.

(В моем коде моделирования строка 17 имеет назначение out1 <= in1 + in2.) Обратите внимание, что симулятор ISIM не поймает эти ошибки, связанные с диапазоном, по умолчанию; вы должны включить опцию «проверка диапазона значений» программного обеспечения. Если этот параметр не включен, симуляция не остановится, и любое значение может быть назначено целому числу, объявленному как ограниченный диапазон.

Обратите внимание, что указание меньшего диапазона не всегда означает, что мы можем представить сигнал с меньшим количеством бит. Например, рассмотрите следующие объявления:

1 signal sig_int1: integer range 0 to 7; 2 signal sig_int2: integer range 6 to 7; 3 signal sig_int3: integer range -8 to 7; 4 signal sig_int1: integer range -8 to 0;

Первые два объявления требуют трехбитового представления, хотя второе объявление имеет меньший диапазон. Аналогичным образом, третье и четвертое объявления должны иметь четыре бита.

Промежуточные вычисления с ограниченными целыми числами

Важно отметить, что хотя симулятор будет проверять диапазон значений, назначенных целому числу, эта проверка происходит только при фактическом присвоении значения, а не во время промежуточных вычислений. Чтобы прояснить это, рассмотрите следующий код:

1 library IEEE; 2 entity IntegerTest1 is 3 port(in1: in integer range 0 to 45; in2: in integer range -45 to 45; 4 out1: out integer range -46 to 89); 5 end IntegerTest1; 6 architecture Behavioral of IntegerTest1 is 7 begin 8 out1 <= (in1 + in2) - 1; 9 end Behavioral;

Предположим, что in1 и in2 равны 45. В строке 8 первая оценка in1 + in2 будет оценена. Таким образом, выражение внутри круглых скобок будет равно 90, которое выходит за пределы диапазона, который может принимать out1. Тем не менее, это промежуточный расчет, и, поскольку пока не задействовано назначение, симулятор не будет проверять диапазон результата. Тогда вычитание будет выполнено, т. Е. 90-1 = 89. Наконец, значение 89, которое теперь находится внутри заданного диапазона, будет присвоено out1. Ниже показано симуляция ISE для приведенного выше кода.

Рисунок 4

В принципе, промежуточные вычисления выполняются с использованием стандартного диапазона целочисленного типа, т. Е. 32 бита. Однако, поскольку это не будет оптимальной реализацией, программное обеспечение для синтеза будет выполнять некоторые оптимизации в зависимости от характера используемых операторов. Например, если промежуточная операция состоит в том, чтобы добавить два целых числа с диапазоном от 0 до 15, результат этого промежуточного вычисления будет иметь достаточное количество бит для представления наибольшего возможного значения, которое равно 30 (более подробно см. Раздел 4.6.4 этой книги).

Предопределенные подтипы Integer

Подтип данного типа ограничивает диапазон типов. Как показано на рисунке 2, «integer» имеет два предопределенных подтипа:

subtype natural is integer range 0 to integer'high; subtype positive is integer range 1 to integer'high;

Значение integer'high представляет наибольшее значение целого числа. «Естественный» подтип создает сигнал, который может принимать все неотрицательные целые числа (т. Е. 0, 1, 2, 3, …), а «положительный» подтип создает сигнал, который может принимать все положительные целые числа (1, 2, 3, …). Хотя эта реализация последовательна в контексте VHDL, имейте в виду, что математическое сообщество не соглашается с тем, включен ли нуль в набор натуральных чисел.

Резюме

- Целочисленный тип данных и его подтипы определены в «стандартном» пакете из библиотеки «std». Тип integer используется для определения объектов, значение которых всегда является целым числом.

- VHDL не указывает точное количество бит для целочисленного типа, но любая реализация VHDL должна поддерживать как минимум 32-разрядную реализацию.

- Мы можем указать диапазон значений, который будет иметь объект типа integer.

- Ограничение диапазона уменьшает ресурсы ПЛИС, необходимые для реализации проекта. Более того, это дает нам возможность проверить ошибки на ранних этапах проектирования.

- Симулятор ISIM по умолчанию не обнаруживает ошибки, связанные с диапазоном; вы должны включить опцию «проверка диапазона значений».

- Эта проверка выполняется только при назначении значения, а не во время промежуточных вычислений.

Чтобы просмотреть полный список моих статей, перейдите на эту страницу.