Типы данных VHDL: некоторые классификации и перечисляемый тип

В этой статье сначала будут рассмотрены классификации типов данных VHDL, а затем обсудим перечислимый тип.

VHDL предоставляет нам несколько опций для типа данных объектов. В предыдущих статьях мы рассмотрели типы std_logic и std_logic_vector. В этой статье сначала будут рассмотрены классификации типов данных VHDL, а затем обсудим перечислимый тип.

Классификация типов данных VHDL

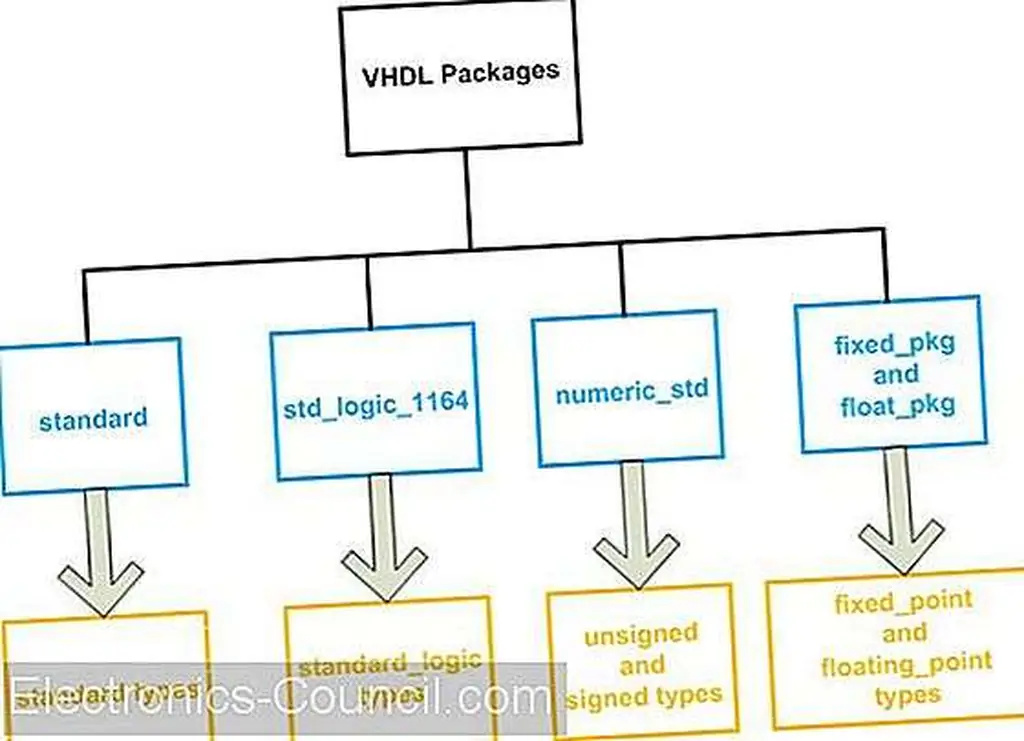

Классификация типов данных VHDL помогает лучше понять эту тему. Общий метод классификации показан на рисунке 1.

Рисунок 1. Каждая группа данных типа VHDL (показана оранжевым цветом) определяется в пакете VHDL (отображается синим цветом)

На этом рисунке классификация типов данных основана на пакете, который определяет тип. Пакеты VHDL показаны на рисунке синим цветом. Каждый из этих пакетов включает определение для некоторых типов данных VHDL (которые показаны оранжевым цветом).

Например, типы данных «std_logic» и «std_logic_vector» являются «стандартными типами». Как показано на рисунке 1, эти типы берутся из пакета «std_logic_1164». Ранее мы видели, что для использования типов данных «std_logic» и «std_logic_vector» нам нужно включить пакет «std_logic_1164» из библиотеки «ieee» в наш код. То есть требуются следующие строки кода.

1 library ieee; 2 use ieee.std_logic_1164.all

Аналогично, перед использованием любого другого типа данных нам нужно сделать соответствующий пакет видимым для кода. В этой статье будут рассмотрены перечисленные типы данных. Существует несколько предопределенных перечисляемых типов в категории «стандартные типы» из «стандартного» пакета. Этот пакет включен в библиотеку VHDL «std». Поэтому, чтобы использовать «стандартные типы», мы должны сделать библиотеку «std» и «стандартный» пакет видимыми для дизайна:

1 library std; 2 use std.standard.all

Однако, поскольку вышеупомянутая библиотека и пакет часто используются, они добавляются в код по умолчанию. Следовательно, нет необходимости явно включать приведенные выше утверждения в наш код. Теперь давайте рассмотрим раздел «стандартные типы» на рисунке 1 более подробно.

Стандартные типы

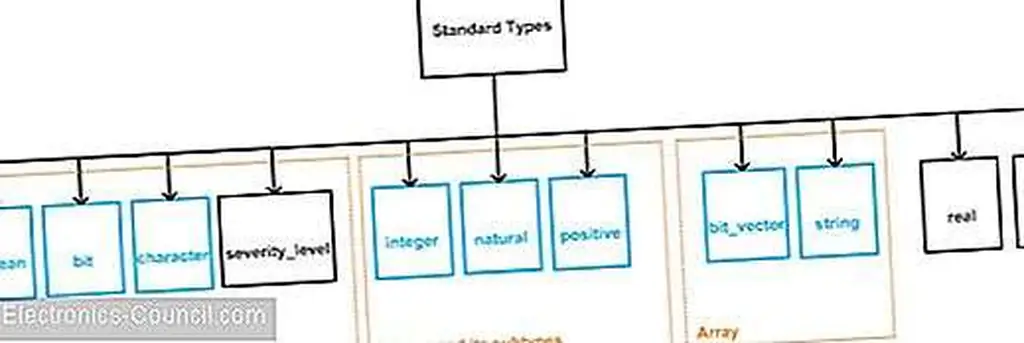

В этой категории есть несколько типов данных. Они показаны на рисунке 2 ниже.

Рисунок 2. Различные типы данных в категории «стандартные типы»

Как показано на этом рисунке, некоторые из этих типов могут быть сгруппированы вместе. Например, типы «boolean», «bit», «character» и «severity_level» могут быть сгруппированы как «перечисленные типы» и т. Д. В этой статье будут объяснены и приведены примеры для типа данных перечисления, а в будущих статьях мы продолжим обсуждение типов данных, показанных на рисунке 2.

Перечисленные типы

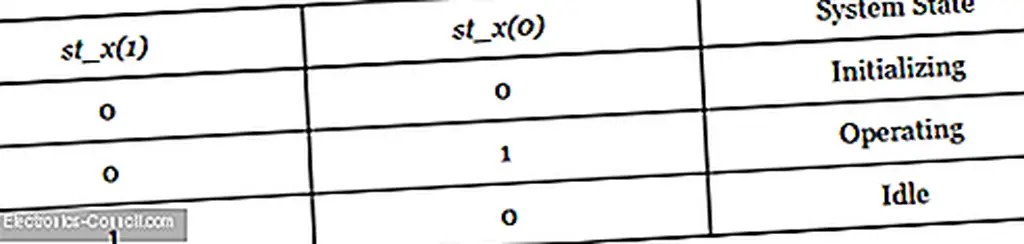

Перечислимые типы данных лучше всего объяснить с помощью примера. Предположим, что вы разрабатываете цифровую систему, которая может находиться в одном из следующих трех состояний: инициализация, работа и простоя. В каждом из этих состояний система выполняет определенные операции. Например, в состоянии инициализации система может обновлять свои входы. В рабочем состоянии он может выполнять некоторые арифметические операции. В режиме ожидания он может перейти в режим с низким энергопотреблением. Нам все равно, какое условие переводит систему из определенного состояния в другое. Для нас важно, как представить состояние системы. Один из способов может представлять состояние системы с использованием двухбитового сигнала, например, st_x. Сигнал st_x может быть определен как двухэлементный тип данных «std_logic_vector» в VHDL. Мы можем рассматривать каждое состояние этого сигнала как код состояния системы; например:

Мы можем постоянно проверять st_x и выполнять требуемые операции на основе состояния системы, которая закодирована в значение st_x. Например, предположим, что в рабочем состоянии предполагается, что система И И два входа a1 и a2 и назначить результат выходному выводу1. Однако в двух других состояниях out1 должен быть равен третьему входу, называемому a3. Следующий код может использоваться для описания поведения выхода out1 (более подробную информацию о параллельных присваиваниях см. В этой статье).

1 with st_x select 2 out1 <= (a1 and a2) when "01", 3 a3 when others;

Проблема с этим методом заключается в том, что нам нужно помнить, какой код используется для представления каждого состояния системы. Это увеличивает вероятность ошибки. Что делать, если мы могли бы использовать слова вместо строки из них и нули для представления состояний системы в нашем коде «st_initializing», «st_operating» и «st_idle». (Вы могли бы использовать разные слова, но, конечно, вы хотите выбрать идентификаторы, которые делают код более понятным и интуитивно понятным.) Однако нам нужно сначала определить тип данных, прежде чем мы определим сигнал этого типа. Логическим выбором для имени этого типа данных будет «sys_state». Сигналы этого типа данных могут принимать три значения: «st_initializing», «st_operating» и «st_idle». Следующий код может использоваться для определения этого нового типа данных.

1 type sys_state is (st_initializing, st_operating, st_idle);

Как вы можете видеть, имя типа данных «sys_state» происходит между ключевыми словами «тип» и «есть». Значения, определенные для этого типа данных, заключены в круглые скобки. Это называется типом данных перечисления, потому что значения перечислены в списке. Теперь мы можем определить сигнал st_x типа «sys_state».

2 signal st_x: sys_state;

Обратите внимание, что st_x может принимать только значения, определенные для типа «sys_state». Теперь, когда у нас есть этот перечислимый тип данных, следующий код может использоваться для описания поведения выхода out1 в приведенном выше примере.

1 with st_x select 2 out1 <= (a1 and a2) when st_operating, 3 a3 when others;

На рисунке 3 показано симуляция Xilinx ISE для вышеупомянутого назначения «с / выбором». Как вы можете видеть, от 200 нс до 400 нс сигнал st_x равен «st_operating», и, следовательно, out1 равен a1 AND a2. Для других значений st_x выход следует за значением a3.

Рисунок 3

Подобно тому, что мы делаем с другими типами данных, мы можем использовать оператор присваивания для назначения значений сигналу st_x. Например, чтобы присвоить значение st_initializing для st_x, мы можем написать:

st_x <= st_initializing;

Несколько перечисленных типов, имеющих общую ценность

Возможно иметь общие значения между двумя различными определяемыми пользователем перечисляемыми типами данных. Например, предположим, что вы определяете следующие перечисленные типы данных для описания состояния двух подсистем в своем дизайне:

1 type sys_stateA is (st_initializing, st_operating, st_idle); 2 type sys_stateB is (st_multiply, st_add, st_idle); 3 signal st_xA: sys_stateA; 4 signal st_xB: sys_stateB;

Как вы можете видеть, буквальное значение «st_idle» является общим для двух типов («literal» относится к значению, которое вставляется дизайнером непосредственно в код VHDL). Однако VHDL считает это приемлемым, потому что мы имеем дело с двумя разными типами данных: «sys_stateA» и «sys_stateB». Если мы назначаем «st_idle» на сигналы st_xA и st_xB, используемый тип данных дает понять, что означает «st_idle». Следовательно, оба следующих назначения будут действительны:

5 st_xA <= st_idle; 6 st_xB <= st_idle;

Начальное значение перечисленных типов

Самый левый элемент списка перечислений будет считаться значением по умолчанию, то есть начальным значением, присвоенным объектам этого типа. Например, значение по умолчанию st_xA и st_xB будет «st_initializing» и «st_multiply» соответственно.

Перечисление символов

Типы перечислений также могут быть определены с использованием символьных литералов. В этом случае мы должны заключить каждый символ в одинарные кавычки. Например, следующий код описывает тип, который имеет три символьных символа.

1 type char_enum is ('c', 'z', '1');

Как показано на рисунке 2, типы «boolean», «bit» и «character» являются предопределенными перечисляемыми типами. Тип «бит» кратко обсуждался в предыдущей статье. Этот тип может принимать либо символ «0», либо «1». Ниже приведены определения типов для предопределенных типов данных «бит» и «булево».

type bit is ('0', '1'); type boolean is (false, true);

Резюме

- Одним из распространенных способов классификации типов данных VHDL является классификация, основанная на пакете, который определяет тип.

- Поскольку библиотека «std» и «стандартный» пакет часто используются, они добавляются в код по умолчанию. Следовательно, нет необходимости явно делать их видимыми для дизайна.

- Типы «boolean», «bit», «character» и «severity_level» являются перечисляемыми типами, доступными в «стандартном» пакете.

- Вместо использования кодирования на уровне бит мы можем использовать перечисленные типы данных для описания дизайна на более абстрактном уровне.

- Возможно иметь общие значения между двумя различными определяемыми пользователем перечисляемыми типами данных.

- Самый левый элемент списка перечислений - это значение по умолчанию, присвоенное объектам перечислимого типа данных.

Чтобы просмотреть полный список моих статей, перейдите на эту страницу.