Провод CMOS

В этом техническом описании представлена простая конфигурация MOSFET, которая может использоваться в качестве переключателя с контролем напряжения.

Вспомогательная информация

Изолированные транзисторы с полевым эффектом (MOSFET)

Обычно мы видим, что МОП-транзисторы расположены со своими источниками и стоками, подключенными либо напрямую, либо через, например, резистор или активную нагрузку - к положительным и отрицательным рельсам питания, причем затвор выступает в качестве входного терминала. Это справедливо в обеих аналоговых схемах, таких как усилитель общего источника и цифровые схемы, такие как вездесущий CMOS-инвертор. Приятно помнить, что MOSFET не ограничивается такими конфигурациями, как эти.

Канал, создаваемый достаточно высоким напряжением затвора к источнику, позволяет протекать ток между терминалами источника и стока, и в этом смысле полевой МОП-транзистор является управляемым по напряжению переключателем. Таким образом, нет закона, который мешает нам использовать источник и утечку в качестве входных и выходных клемм, при этом управляющее напряжение подается на затвор.

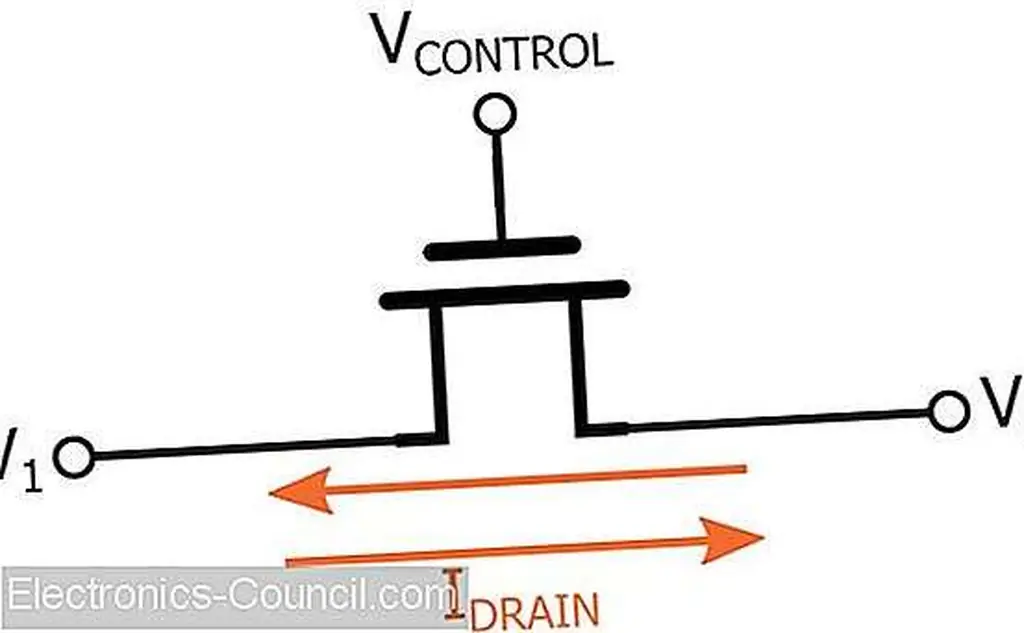

Один транзистор NMOS (или PMOS) может использоваться в качестве переключателя, управляемого напряжением. «Схема» (на самом деле это всего лишь один транзистор):

Обратите внимание, что я удалил стрелку, которая обычно идентифицирует источник. Это связано с тем, что исходный терминал фактически изменяется в зависимости от того, является ли V 1 выше V 2 или V 2 выше, чем V 1. Кроме того, использование V 1 и V 2 вместо V IN и V OUT призвано подчеркнуть, что этот единственный NMOS-транзистор действительно может проводить ток в обоих направлениях.

Как вы, вероятно, ожидали, эта схема далека от идеального переключателя. Одной из проблем является напряжение источника: ток через MOSFET зависит от напряжения источника, а напряжение источника зависит от любого сигнала, проходящего через коммутатор. Действительно, если ворота управляются драйвером, который не может превышать V DD, транзистор может передавать сигналы только до V DD за вычетом порогового напряжения. Это ограничение порогового напряжения еще больше ухудшается благодаря эффекту тела, который вступает в игру, когда клеммы источника и тела FET не имеют одинакового потенциала.

Когда вы анализируете и обдумываете этот переключатель, вы распознаете определенную асимметрию. Например, если мы используем этот переключатель для транзисторной логики, NMOS может эффективно передавать сигнал с логическим низким, но не полный логический сигнал. Возможно ли изменить схему таким образом, чтобы устранить эту асимметрию "" src = "// www.allaboutcircuits.com/uploads/articles/TB_CTG_2_2.jpg" />

Здесь мы имеем PMOS параллельно с NMOS; Я использовал «инвертированный» круг для идентификации транзистора PMOS. Обратите внимание, что управляющий сигнал, применяемый к PMOS, является дополнением к управляющему сигналу, примененному к NMOS; это напоминает инвертор CMOS, где логическое высокое напряжение включает NMOS, а логическое низкое напряжение включает PMOS.

Этот шлюз передачи CMOS является синергетической системой - NMOS обеспечивает хорошую работу коммутатора в благоприятных для себя условиях, но не для PMOS, а PMOS обеспечивает хорошую работу коммутатора в благоприятных для себя условиях, но не для NMOS. Результатом является простой, но эффективный двунаправленный переключатель с напряжением, который подходит как для аналоговых, так и для цифровых приложений.