RISC-V: преобразование разработки SoC-устройств, объединяющих FPGA и микроконтроллеры

До недавнего времени разработчики, интегрировавшие FPGA-ткань с микроконтроллером, были сильно ограничены в выборе вариантов лицензирования IP-адресов, с закрытой экосистемой ядер и инструментов и практически отсутствием возможности переноса программного обеспечения на другие архитектуры.

Все это изменилось с помощью открытой архитектуры набора инструкций RISC-V (ISA), которая устраняет гонорары роялти и другие ограничения лицензионных IP-ядер, создавая новый способ разработки и надежных систем на чипе (SoC) в сегодняшнем быстром развивающиеся рынки. Разработчики, которые принимают RISC-V, имеют ценные возможности для улучшения переносимости дизайна, сокращения и сохранения инвестиций в программное обеспечение и перспективных проектов сегодня и в будущем. Для многих различных приложений использование инструментов с открытым исходным кодом с ядром RISC-V в FPGA является неотразимым выбором.

Гибкий фонд для инноваций

Процессор RISC-V основан не на архитектуре, а на фиксированном наборе команд (ISA). Конструкция микро-архитектуры процессора является гибкой; поставщики могут свободно использовать любую архитектуру, которую они считают лучшим для своего приложения.

Чтобы обеспечить широкое использование, некоммерческая организация RISC-V, контролируемая ее членами, заморозила набор инструкций в 2014 году, чтобы рынок мог диктовать свои процессорные архитектуры. Используя возможности сообщества с открытым исходным кодом, разработчики, которые используют решение микроконтроллера RISC-V в FPGA, получают преимущества от аппаратной переносимости, предсказуемости программного обеспечения и широких инновационных возможностей.

портативность

Конструкции, которые могут разгоняться в большой объем, выиграют от мобильности RISC-V. Разработчики могут начать дизайн в FPGA с мягкой версией ворот ядра RISC-V, а затем начать отправку продукта (например, тепловой камеры).

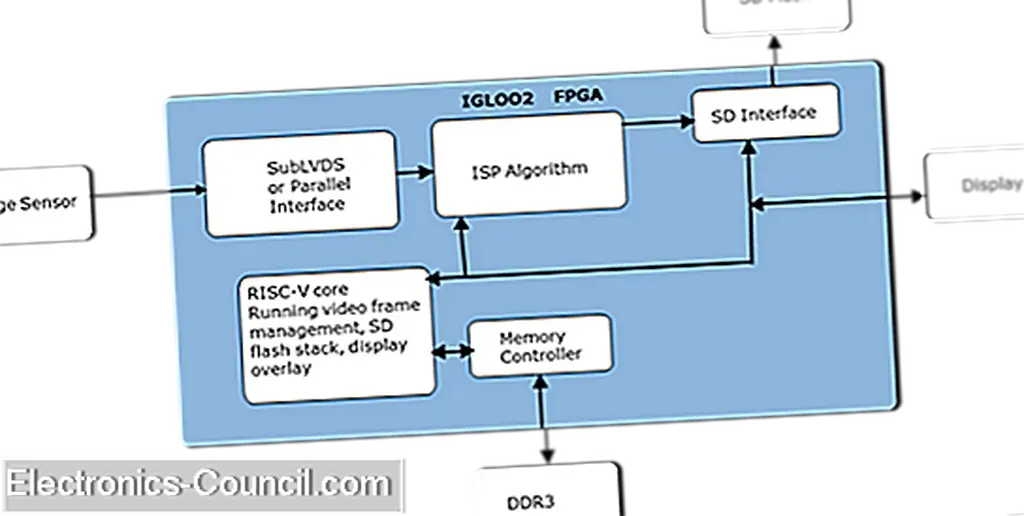

Рисунок 1. Блок-схема камеры с тепловым изображением

Ядро RISC-V в камере реализует все традиционные функции, которые поддерживает микроконтроллер: он сначала настраивает датчик изображения и периодически обновляет настройки, когда требуются настройки. Ядро RISC-V также может запускать стек хранения внешней памяти для настройки передачи изображений или видеокадров. Поскольку программное обеспечение будет полностью переносимым на всех устройствах с ядром RISC-V, это создаст «неоплачиваемый» код уровня передачи подсистемы процессора (RTL), который может быть реализован на любом оборудовании. Итак, если объемы этой камеры достигают достаточно высоких уровней, просто перенастройте RTL-источник в ASIC, не выплачивая никаких юридических или роялти.

Стабильность программного обеспечения

Долговечность является основным преимуществом RISC-V. Разработчики могут рассчитывать на фиксированную ISA и сохранять инвестиции в программное обеспечение. Промышленные конструкции, которые часто создаются в течение нескольких лет, а иногда и десятилетий, могут зависеть от непрерывности программного обеспечения. С приведенным выше примером камеры программный код, написанный и проверенный для первоначального решения, может быть запущен на любом ядре RISC-V в будущем. Первоначальное производство можно выполнить с помощью мягкого ядра RISC-V в FPGA IGLOO2, и код будет полностью совместим при создании ASIC.

Инновации с открытым исходным кодом

Появление Linux как доминирующей операционной системы на встроенном рынке является доказательством силы открытого источника. Можно подумать о нововведениях RISC-V следующим образом: RISC-V - это аппаратное проектирование того, что Linux для программного обеспечения. Уже существуют инструменты с открытым исходным кодом для использования с RISC-V, такие как графические интерфейсы Eclipse, операционные системы RTOS, инструменты моделирования и отладочное программное обеспечение. Сообщество с открытым исходным кодом дополнительно приносит пользу пользователям RISC-V, поскольку темпы инноваций могут ускориться благодаря тому, что многие дополнительные разработчики внедряют ядра и программные средства. Пользовательские микро-архитектуры могут быть созданы, а исправления ошибок / исправления безопасности могут быть идентифицированы гораздо быстрее, чем с проприетарной архитектурой процессора.

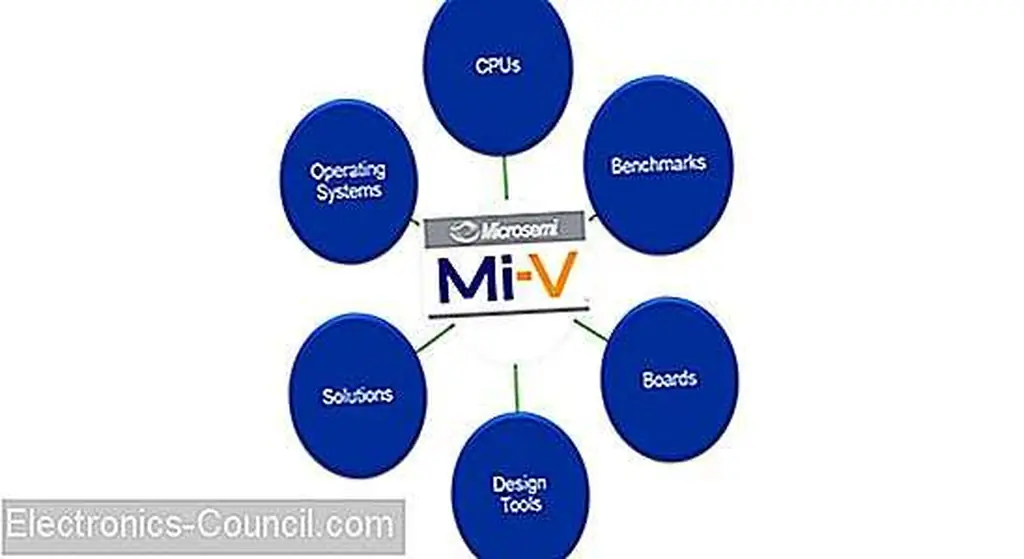

В качестве примера можно привести недавно выпущенную Microsemi экосистему RISC-V под названием Mi-V. В экосистеме Mi-V есть первая открытая архитектура RISC-V на базе FPGA и комплексное решение для среды разработки (IDE), называемое SoftConsole.

Рисунок 2. Microsi Mi-V RISC-V Ecosystem

SoftConsole - это среда IDE на основе Eclipse, размещенная на платформе Linux или Windows, для обеспечения полной поддержки разработки, включая компилятор C или C + и возможности полного отладки. Дизайнеры могут разрабатывать для IP-ядра RISC-V в нескольких FPGA с флэш-памятью, включая устройства Microsemi PolarFire и IGLOO2, а также ядра RISC-V от других производителей. Встроенные инженеры могут использовать преимущества Mi-V RISC-V IP в своих конструкциях FPGA, используя Libero SoC Design Suite. Это простое в использовании программное обеспечение для разработки позволяет разработчикам еще больше оптимизировать ядро RISC-V RTL для их конкретного применения.

Дизайнеры, которые хотят интегрировать микроконтроллер в FPGA, теперь имеют убедительное решение с RISC-V. Преимущества переносимости дизайна, стабильности программного обеспечения и инноваций с открытым исходным кодом могут принести пользу практически каждому приложению. Клиенты также могут рассчитывать на фиксированную ISA для обеспечения совместимости программного обеспечения и долговечности архитектуры. Использование ядра RISC-V открывает новое поколение инноваций для дизайнеров SoC.

Отраслевые статьи - это форма контента, которая позволяет отраслевым партнерам делиться полезными новостями, сообщениями и технологиями с читателями All About Circuits таким образом, что редакционный контент не очень подходит. Все отраслевые статьи подчиняются строгим редакционным правилам с целью предоставления читателям полезных новостей, технических знаний или историй. Точки зрения и мнения, выраженные в отраслевых статьях, являются точками партнера, а не обязательно для All About Circuits или его авторов.