Решение энергетических задач интеграции нескольких интерфейсов GbE

Хотя FPGA часто используются для выполнения функций моста для Ethernet и Gigabit Ethernet (GbE), они не часто ассоциируются с низким энергопотреблением. Вот исследование того, как новые ПЛИС среднего диапазона решают эту проблему в эпоху растущего спроса на Ethernet и уменьшения форм-факторов.

В сегодняшнем мире, все более тесно связанный, растет спрос на Ethernet и дополнительные линии Gigabit Ethernet (GbE) в различных промышленных, коммуникационных и информационных центрах. ПЛИС часто используются для выполнения функций моста для интерфейсов GbE из-за их низких затрат на проектирование, высокой производительности, скорости выхода на рынок, повторного использования и комбинации быстрых и гибких полевых обновлений.

До недавнего времени они не знали о низком энергопотреблении и простоте использования, которые нужны дизайнерам, если они хотят использовать единую FPGA для создания современных гибридных решений, включающих множество различных интерфейсов 10G и 1G. Все это изменяется с последней итерацией ПЛИС среднего диапазона, которые обеспечивают несколько портов GbE в одном устройстве и могут реализовывать энергоэффективные интерфейсы 1G без необходимости использования трансиверов, что значительно снижает энергопотребление.

Предназначен для мощных интерфейсов GbE

Традиционные средние ПЛИС со скоростью 10 Мбит / с, 100 Мбит / с, 1 Гбит / с и 10 Гбит / с помогли увеличить спрос на дополнительные соединения в одном продукте. Проблема с этими FPGA на верхнем конце с интерфейсами 1G заключалась в том, что необходимы трансиверы, увеличивая мощность и размер пакета. Это уже не так с появлением новых сред FPGA среднего уровня, которые предлагают более масштабируемую возможность использования универсальных входных-выходов (GPIO) для реализации нескольких интерфейсов GbE. Это более энергоэффективно, а также позволяет разработчикам резервировать использование приемопередатчиков для высокоскоростных системных реализаций с использованием протоколов, таких как Ethernet, CPRI, JESD204B и PCIe 10 Гбит / с.

GPIO легко использовать в современных FPGA-устройствах среднего уровня. Они поддерживаются высоко настраиваемыми схемами приемника и драйвера за каждым выводом, а также могут динамически регулировать задержки сигнала (в том числе связанные с отношениями часовых передач). Они реализуют функциональные возможности цепей синхронизации и восстановления данных (CDR) для каждого типа и поддерживают популярные стандарты ввода-вывода и терминалы.

Внедрение системы

Сегодня многие функции интерфейса GbE могут быть реализованы путем настройки пары дифференциальных выходных выводов GPIO и пары дифференциальных входных контактов GPIO. Эти функции включают в себя сериализатор, де-сериализатор и CDR, а также функциональность бит-скольжения для выравнивания символов. Закрепленные интерфейсы схем GPIO легко взаимодействуют с подслоем физического кодирования (PCS), управлением доступом к среде (MAC) и более высокими уровнями, реализованными в FPGA-матрице, что дает высоко настраиваемое решение GbE. GPIO поддерживают широкий диапазон стандартов ввода / вывода, работающих с источниками питания от 1, 2 до 3, 3 В, со скоростью до 1, 066 Гбит / с для нестандартных стандартов и 1, 25 Гбит / с с использованием дифференциальных стандартов.

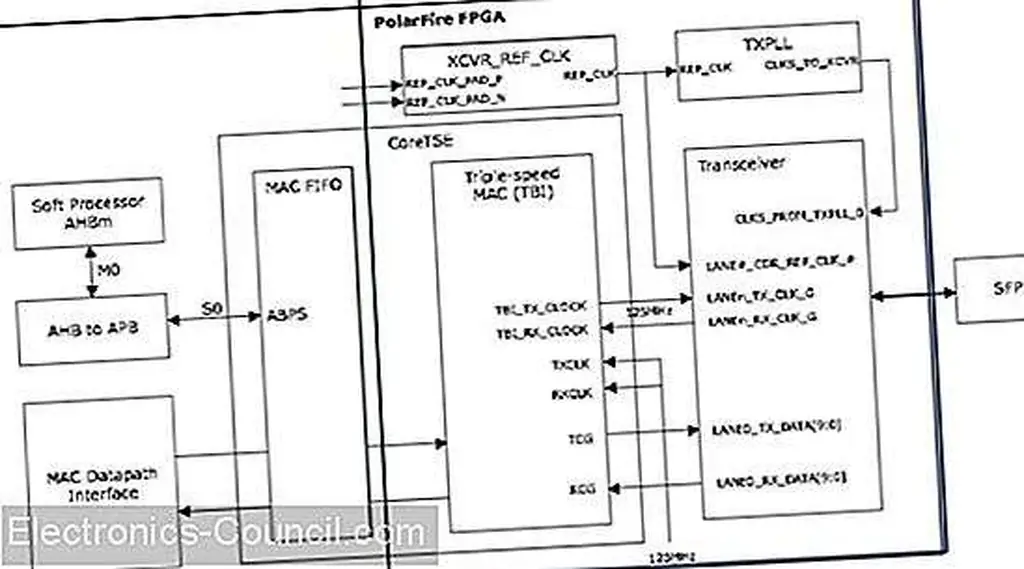

На следующих блок-диаграммах высокого уровня показано, как одно и то же устройство FPGA может использоваться для реализации двух разных решений 1 GbE, один по GPIO и другой по приемопередатчикам.

Рисунок 1. Реализация 1 GbE по GPIO с использованием FPGA Microsemi PolarFire

Рисунок 2. 1 Реализация GbE по трансиверу с использованием FPGA Microsemi PolarFire

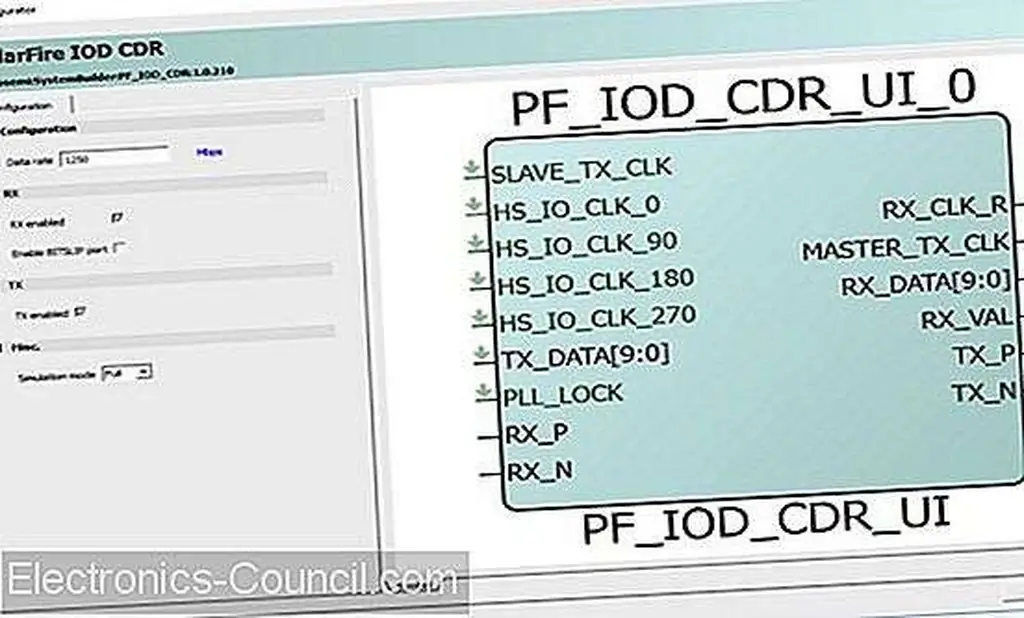

В первом примере для реализации функциональных возможностей интерфейса по сравнению с GPIO используются программные средства проектирования FPGA на основе чипа (SoC). IP-интерфейс FPGA Ethernet включает в себя ядро, которое объединяет GPIO и CDR, которые доступны на каждой полосе банковского обслуживания GPIO устройства для обеспечения синхронизации часов и данных для скорости передачи данных 1 Гбит. На каждой стороне устройства может быть более одного из этих сердечников, передающих высокоскоростные сигналы от контура фазовой автоподстройки частоты (ФАПЧ), расположенного в углу матрицы FPGA. Ядро GPIO создается из каталога программного обеспечения, а затем настраивается путем выбора скорости передачи данных (в данном случае 1250 Мбит / с). Он объединяется с базой PLL и логикой передачи и приема MAC для завершения проектирования. Снимок ядра GPIO показан на диаграмме ниже.

Рисунок 3. Конфигуратор графического интерфейса GPIO

Сравнение мощности

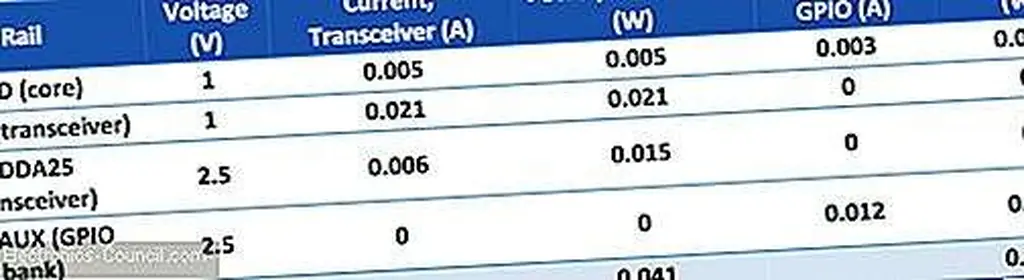

Несмотря на то, что нет никакой разницы в доступности материальных ресурсов между созданием интерфейса интерфейса Ethernet для реализации GbE-over-GPIO по сравнению с созданием подлинности ядра трансивера, PLL приемопередатчика и опорными тактами для реализации приемопередатчика, сравнительная эффективность мощности - это другая история. GPIO CDR потребляют меньше энергии, чем приемопередатчик, тем самым снижая потребление энергии для приложений, использующих несколько ссылок GbE. Чтобы сравнить номера мощности приемопередатчика на основе реализации на основе GPIO, мы использовали данные о мощности (начальная расчетная информация на основе моделирования) для устройства PolarFire MPF300T, пакет FCG1152.

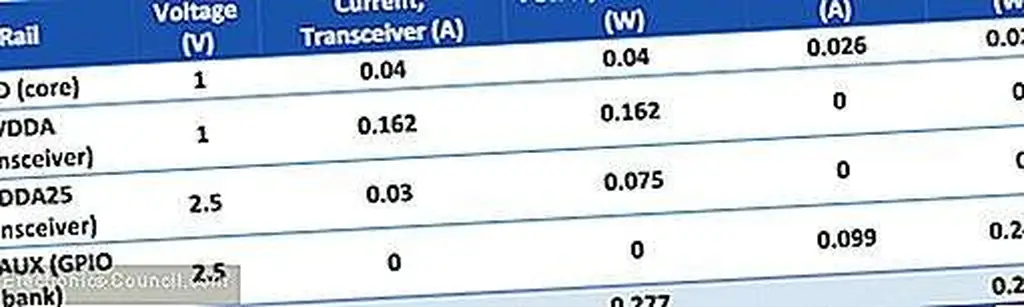

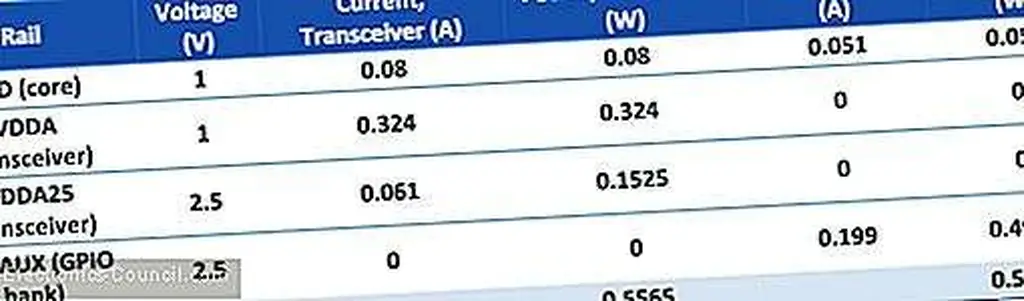

В приведенных ниже таблицах приведена общая мощность, потребляемая различными рельсами для одной полосы GPIO или одной полосы трансивера, восемь полос GPIO или восемь полос приемопередатчика и 16 полос GPIO или шестнадцать полос приемопередатчика.

Таблица 1: Сравнение мощности - 1 полоса трансивера против 1 полосы GPIO

Таблица 2: Сравнение мощности - 8 полос трансивера и 8 полос GPIO

Таблица 3: Сравнение мощности - 16 полос приемопередатчика против 16 полос GPIO

SGMII через GPIO предоставляет дополнительные преимущества

Самые последние FPGA среднего уровня также предоставляют возможность поддерживать многочисленные линии Ethernet 1 Гбит / с, реализуя независимый интерфейс Serial Gigabit Media (SGMII) по сравнению с GPIO.

В прошлом разработчики могли использовать только ПЛИС среднего диапазона для реализации SGMII через GPIO, если они использовали более крупные пакеты с дополнительными приемопередатчиками. Зачастую им приходилось переходить на FPGA с более высоким количеством логических элементов (LE), увеличивая как потребление энергии, так и стоимость. Однако с новейшими FPGA среднего уровня, легко реализовать SGMII-over-GPIO, и требуется меньше блоков конфигурации по сравнению с реализацией SGMII с трансивером. Реализация на основе GPIO использует общую PLL для нескольких дорожек и банков, в то время как для приемопередатчика требуется выделенный PLL, что приводит к снижению общей мощности с GPIO.

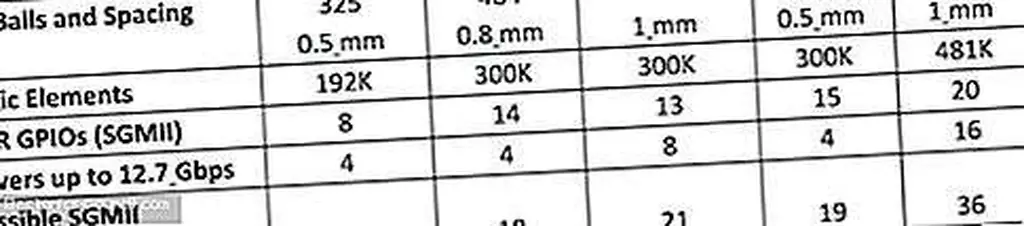

Рассматривая сравнение ресурсов ниже, очевидно, что больше портов может быть реализовано с помощью GPIO, чем приемопередатчиком. Дополнительным преимуществом использования GPIO является то, что полосы скоростного трансивера могут быть зарезервированы для других протоколов, таких как 10 GbE, CPRI, Interlaken и PCIe.

Таблица 4: Сравнение ресурсов

Предоставляемые данные предназначены для FPGA Microsemi PolarFire

ПЛИС могут быть идеальными решениями для упаковки большего количества интерфейсов GbE в сегодняшние более мелкие следы системы, если они могут удовлетворить все более сложные требования к мощности. Последние средние ПЛИС достигают этого, предлагая возможность реализовать эту функциональность интерфейса над GPIO, используя ядро IP, которое объединяет GPIO с CDR.

Предоставляя несколько портов GbE на одном устройстве без необходимости приемопередатчиков, этот подход значительно снижает потребление энергии, упрощая реализацию гибридного высокопроизводительного решения с несколькими портами сопряжения 10G и 1G и масштабируя плотность портов с очень низким инкрементным увеличение общей мощности. Этот подход особенно привлекателен для разработчиков маломощных модульных модульных модулей (SFP), специализированных промышленных коммутаторов, масштабируемых коммутаторов L2 / L3 и других систем, которые могут использовать преимущества малых форм-факторов и большого количества недорогих, низких - мощные и эффективные GPIO, которые доступны в современных решениях FPGA среднего уровня.

Отраслевые статьи - это форма контента, которая позволяет отраслевым партнерам делиться полезными новостями, сообщениями и технологиями с читателями All About Circuits таким образом, что редакционный контент не очень подходит. Все отраслевые статьи подчиняются строгим редакционным правилам с целью предоставления читателям полезных новостей, технических знаний или историй. Точки зрения и мнения, выраженные в отраслевых статьях, являются точками партнера, а не обязательно для All About Circuits или его авторов.