Внедрение конечной машины в VHDL

Немного фона

В цифровых системах существуют два основных типа схем. Первый тип - схемы комбинационных логических схем. В комбинационных логических схемах выходы зависят исключительно от входов. Примеры схем комбинационных логических схем включают сумматоры, кодеры и мультиплексоры. Например, в сумматорах выход представляет собой просто сумму входов; не имеет значения, какой из предыдущих входов или выходов был. Второй тип цифровых логических схем - последовательные логические схемы. В последовательных логических схемах выходы зависят не только от входов, но и от текущего состояния системы (т. Е. Значений выходов и любых внутренних сигналов или переменных). Последовательные логические схемы варьируются по сложности от простых счетчиков, которые переходят из одного состояния в другое в базовой последовательности (например, 0, 1, 2, 3 … 0, 1, 2, 3 …) в схемы очень крупного масштаба, такие как микропроцессоры с миллионами из разных состояний или более. Основное внимание в этой статье будет посвящено представлению последовательных логических схем как машин конечного состояния и как преобразовать эти машины конечного состояния в язык описания аппаратных средств VHDL.

Последовательные логические системы - это конечные автоматы (FSM). Как FSM, они состоят из набора состояний, некоторых входов, некоторых выходов и набора правил для перехода из состояния в состояние. При разработке цифровой системы очень часто начинается определение того, как система работает с моделью конечных автоматов. Этот шаг проектирования позволяет дизайнеру подумать о дизайне с точки зрения высокого уровня, не задумываясь о том, какое оборудование будет реализовано в системе или какие инструменты проектирования потребуются для реализации дизайна. Как только FSM полностью сконструирован, если он хорошо спроектирован, легко написать проект на языке описания аппаратных средств (например, Verilog или VHDL) для реализации на цифровой ИС (интегральная схема).

В этой статье мы рассмотрим процесс проектирования цифровой системы, сначала определив проблему проектирования, во-вторых, создадим вычислительную модель системы как конечный конечный автомат и, в-третьих, переведем FSM в язык описания аппаратных средств VHDL. (VHDL на самом деле является двойным аббревиатурой. VHDL означает VHSIC Hardware Description Language и VHSIC - это высокоскоростная интегральная схема).

Читатели должны иметь некоторый опыт работы с цифровыми схемами и ИС. Они также должны иметь базовое понимание VHDL или, по крайней мере, иметь некоторый опыт чтения структурированного компьютерного кода. Опыт работы с компьютерным кодом поможет вам распознать некоторые структуры и конструкции VHDL, но следует отметить, что VHDL не является языком программирования; это язык описания аппаратного обеспечения (HDL). Другими словами, заявления, которые вы пишете, собираются создавать оборудование (ворота, флип-флопы и т. Д.) В проектируемой системе.

Конечный автомат

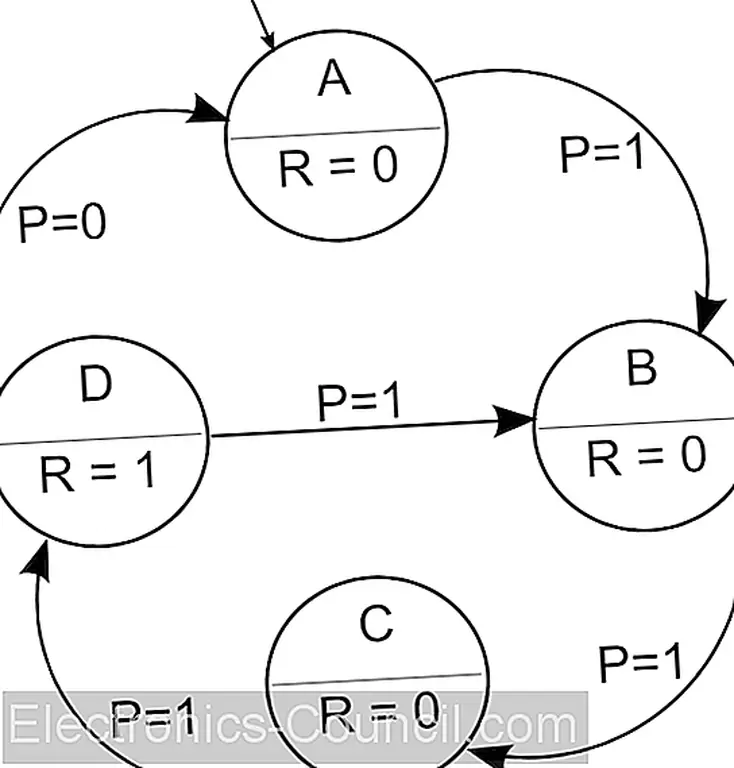

Система, которая будет разработана, очень проста, и ее цель - представить идею преобразования FSM в VHDL. Этот FSM имеет четыре состояния: A, B, C и D. Система имеет один входной сигнал под названием P, а значение P определяет, в каком состоянии система переходит к следующему. Система изменяет состояние от A до B до C до D, пока вход P высокий (1). Если P низкий, а система находится в состоянии A, B или C, состояние не изменяется. Если система находится в состоянии D, она изменяется на B, если P - высокая, а A - на P. Система также имеет выход, называемый R, который равен 1, если в состоянии D, в противном случае это 0. Рисунок 1 - диаграмма для FSM, но сначала здесь несколько примечаний об этой диаграмме:

- Кружки представляют состояния

- Стрелки между кругами представляют собой правила перехода из состояния в состояние. Например, в этой системе конечный автомат переходит из состояния A в состояние B, если вход P равен 1 (иначе он остается в состоянии A)

- Информация под линией в круге представляет собой выходное значение, когда в каждом состоянии.

- Стрелка, идущая от «никуда» до А, указывает, что А - начальное состояние.

Рисунок 1. Простая машина конечного состояния

Этот полностью определенный конечный автомат может быть легко преобразован в VHDL. Важно помнить, что при написании кода VHDL, что вы делаете, описывается, как вы хотите, чтобы аппаратное обеспечение (то есть цифровые ворота) было реализовано. Так, например, когда вы определяете набор состояний, таких как A, B, C и D в этой системе, эти состояния будут представлены битами, а точнее - выходом флип-флопов. В системе с четырьмя состояниями, подобными этой, можно было бы представить те четыре состояния с двумя битами (2 флип-флопа). Есть и другие способы, которыми могли бы быть представлены государства. Одним из таких способов было бы использовать четыре бита, где каждый бит представляет состояние, но только один бит может быть включен одновременно. Таким образом, A будет представлено 0001, B на 0010, C на 0100 и D на 1000. Одной из хороших особенностей использования языка описания аппаратного обеспечения высокого уровня является то, что вы часто можете игнорировать этот уровень детализации.

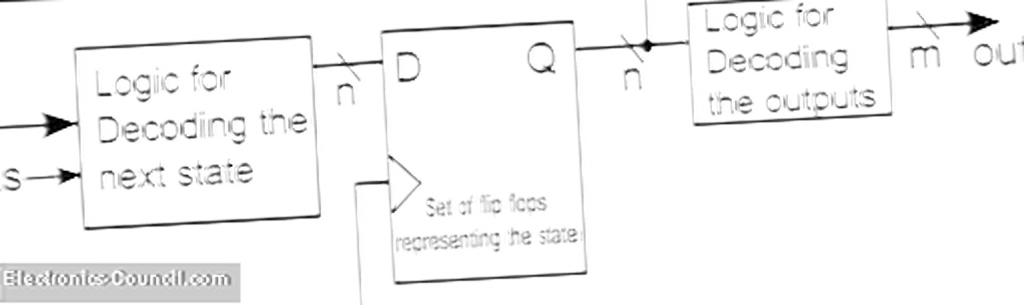

На рисунке 2 показана общая идея аппаратной схемы, которая будет создана, когда код VHDL будет синтезирован для создания аппаратного обеспечения.

Рисунок 2. Представление блочной диаграммы логики, созданной для машины состояния

Эта диаграмма показывает, что существует набор n флип-флопов, которые представляют состояние. Существует также некоторая логика, которая использует выход триггеров и входов в систему для определения следующего состояния. Наконец, существует некоторая логика, которая декодирует выходные значения триггеров для создания выходных сигналов m.

Опять же, при использовании HDL вы часто можете игнорировать этот уровень детализации в своем дизайне. По-прежнему важно понять, какая схема создана вашим HDL, потому что может наступить время, когда вам нужно подсчитывать и минимизировать логические логические номера в вашем дизайне. С пониманием того, что создано вашими заявлениями HDL, вы можете проектировать, чтобы свести к минимуму создание ворот.

Внедрение дизайна VHDL

Первым шагом в написании VHDL для этого FSM является определение объекта VHDL. Объект VHDL описывает внешний интерфейс проектируемой системы, который включает в себя входы, выходы и имя объекта. Общая форма объекта выглядит следующим образом:

ENTITY -entityName- isPORT (-portName1-: -signalDirection- -type-;-portName2-: -signalDirection- -type-;----portName_n-: -signalDirection- -type-; END -entityName-;--Note: user defined entries are between the dashes

Используя этот шаблон, можно создать объект для простого FSM. Имя объекта будет SimpleFSM, входы представляют собой тактовый сигнал, сигнал сброса и сигнал P, а выход - R- сигнал. Следует отметить, что тактовый сигнал представляет собой периодический сигнал с высоким низким уровнем, который управляет синхронизацией этой синхронной системы. Любая синхронная система имеет один управляющий тактовый сигнал, который синхронизирует все блоки в системе, делая их изменения в одно и то же время.

Объединение всей информации дает объект SimpleFSM, который выглядит следующим образом:

ENTITY SimpleFSM is PORT (clock: IN STD_LOGIC;P: IN STD_LOGIC;reset: IN STD_LOGIC;R: OUT STD_LOGIC); END SimpleFSM;

Одна заключительная заметка о сущности заключается в том, что все входы и выходы являются одиночными битами и поэтому могут использовать тип данных std_logic, который является стандартным типом в VHDL для однобитовых сигналов.

Следующий шаг - определить функциональность объекта; этот блок VHDL называется архитектурой. Функциональность, которую мы реализуем, - это конечная машина, определенная на рисунке 1. В приведенном ниже примере показан код, который потребуется для реализации SimpleFSM. Хотя этот код специфичен для SimpleFSM, я опишу, что делает каждый из разделов кода так, что это будет простой процесс для замены этого кода кодом для вашего собственного конечного автомата.

-- Architecture definition for the SimpleFSM entity Architecture RTL of SimpleFSM is TYPE State_type IS (A, B, C, D); -- Define the statesSIGNAL State: State_Type; -- Create a signal that uses-- the different states BEGIN PROCESS (clock, reset) BEGIN If (reset = '1') THEN -- Upon reset, set the state to AState <= A; ELSIF rising_edge(clock) THEN -- if there is a rising edge of the -- clock, then do the stuff below-- The CASE statement checks the value of the State variable, -- and based on the value and any other control signals, changes-- to a new state. CASE State IS -- If the current state is A and P is set to 1, then the -- next state is B WHEN A => IF P="1" THENState <= B;END IF; -- If the current state is B and P is set to 1, then the -- next state is C WHEN B => IF P="1" THENState <= C;END IF; -- If the current state is C and P is set to 1, then the -- next state is D WHEN C => IF P="1" THENState <= D;END IF; -- If the current state is D and P is set to 1, then the -- next state is B. -- If the current state is D and P is set to 0, then the -- next state is A. WHEN D=> IF P="1" THENState <= B; ELSEState State <= A;END CASE; END IF; END PROCESS;-- Decode the current state to create the output -- if the current state is D, R is 1 otherwise R is 0 R <= '1' WHEN State=D ELSE '0'; END rtl;

Это весь код, необходимый для конечного автомата. Теперь давайте рассмотрим некоторые детали кода архитектуры.

В определении архитектуры указано:

Architecture RTL of SimpleFSM is

Это утверждение является стандартным для архитектуры VHDL и в основном описывает уровень абстракции, который будет описан в архитектуре. RTL, который обозначает уровень передачи регистров, является средним уровнем абстракции.

Behavioral - это самый высокий уровень абстракции, и при написании поведенческого кода вам просто нужно определить отношения между входами и выходами, не указав ничего о том, как эти отношения будут реализованы. Иногда поведенческие описания слишком высоки и фактически не могут быть синтезированы в аппаратное обеспечение. Если вы выполняете симуляцию и просто нуждаетесь в блоке, чтобы вести себя определенным образом, тогда поведенческая модель будет адекватной.

Структурный код - это самый низкий уровень абстракции. При написании структурного кода вы описываете, как структуры низкого уровня (например, логические ворота) соединяются вместе, чтобы дать системе, которую вы хотите. Если вам нужен точный контроль над логическими воротами, которые будут созданы, структурная модель - это то, что вам нужно.

RTL помещается посередине. В нем конкретно описываются отношения между входами и выходами, описывающие, как данные перемещаются между регистрами в аппаратном обеспечении. Описание RTL реализуется в аппаратном обеспечении. Для этого конкретного примера не очень важно понимать нюансы типа архитектуры (поведенческий, RTL или структурный), вам просто нужно определить его как нечто.

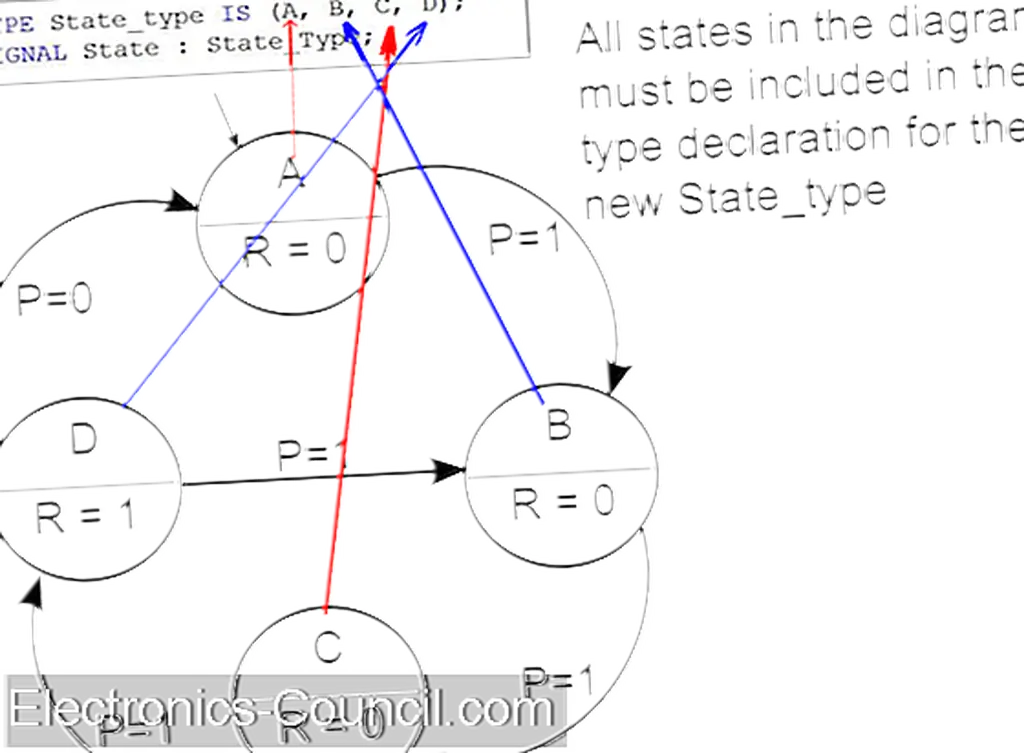

Следующий блок определяет состояния и создает сигнал, который будет иметь определенное состояние в качестве его значения. Должно быть взаимно однозначное отображение состояний, перечисленных здесь, в состояния, представленные кружками на диаграмме FSM.

TYPE State_type IS (A, B, C, D); -- the 4 different statesSIGNAL State: State_Type; -- Create a signal that uses -- the 4 different states

Следующим утверждением является начало процесса VHDL с синхронизацией сигналов и сброс в списке чувствительности

PROCESS (clock, reset) BEGIN If (reset = '1') THEN -- Upon reset, set the state to AState <= A;ELSIF rising_edge(clock) THEN

Опять же, есть много подробностей о объявлениях процессов, которые могут быть проигнорированы для этой статьи. Все, что вам нужно понять, это то, что при разработке уровня RTL этот процесс создаст регистр для всех сигналов, у которых есть назначения в процессе. В этом случае только сигнал состояния имеет назначение, поэтому будет создан регистр, состоящий из достаточного количества флип-флопов для представления значения состояния. Этот регистр будет синхронизирован с нарастающим фронтом часов и будет асинхронно перезагружен с помощью сигнала сброса. Общее визуальное представление схемы, которое будет создано процессом, можно увидеть на рисунке 2.

Тело кода, следующего за

rising_edge(clock)

является оператором case VHDL, который будет синтезирован в логику для управления тем, какое значение изменяется на каждом фронте часов. Например, утверждение

WHEN A => IF P="1" THEN State <= B; END IF;

означает, что если State имеет значение A, тогда, если сигнал P равен 1, измените состояние на B на фронте нарастающего фронта.

Последнее утверждение в этом случае

WHEN others =>State <= A;

Этот оператор является оператором catch-all, чтобы убедиться, что если State каким-то образом имеет значение, не равное A, B, C или D, тогда оно будет сброшено до значения A.

Заключительный раздел кода выполняется вне процесса и создает блок комбинационной логики.

R <= '1' WHEN State=D ELSE '0';

То, что делает этот оператор, - это определение значения выхода R. R будет 1, если состояние D, и оно будет 0 во всех других состояниях. Здесь следует отметить, что выход этого конечного автомата зависит только от состояния. Государственные машины, в которых настоящее состояние является единственным, определяющим выход, называются государственными машинами Мура. Другая широкая категория государственных машин - это та, где выход зависит не только от текущего состояния, но и от входных данных. Этот тип конечного автомата называется машиной состояния Мили. На практике, как правило, неважно, какой тип конечного автомата вы используете, даже не важно, знаете ли вы, какой именно государственный автомат вы используете. Все, что имеет значение, - это то, что вы реализуете конечный автомат, как вы его определили.

Последние несколько шагов при разработке этой системы включают в себя моделирование системы, чтобы убедиться, что она выполняет то, что она должна делать, а затем, наконец, синтезировать аппаратное обеспечение для реализации на физической системе (CPLD, FPGA, ASIC и т. Д.),

Резюме

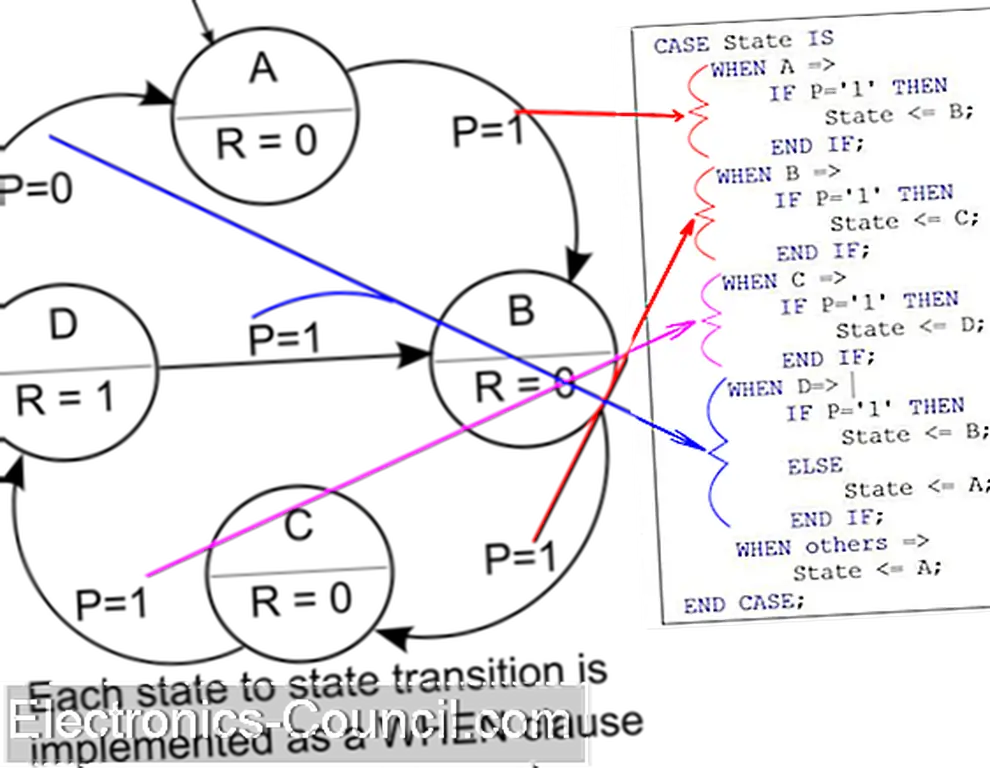

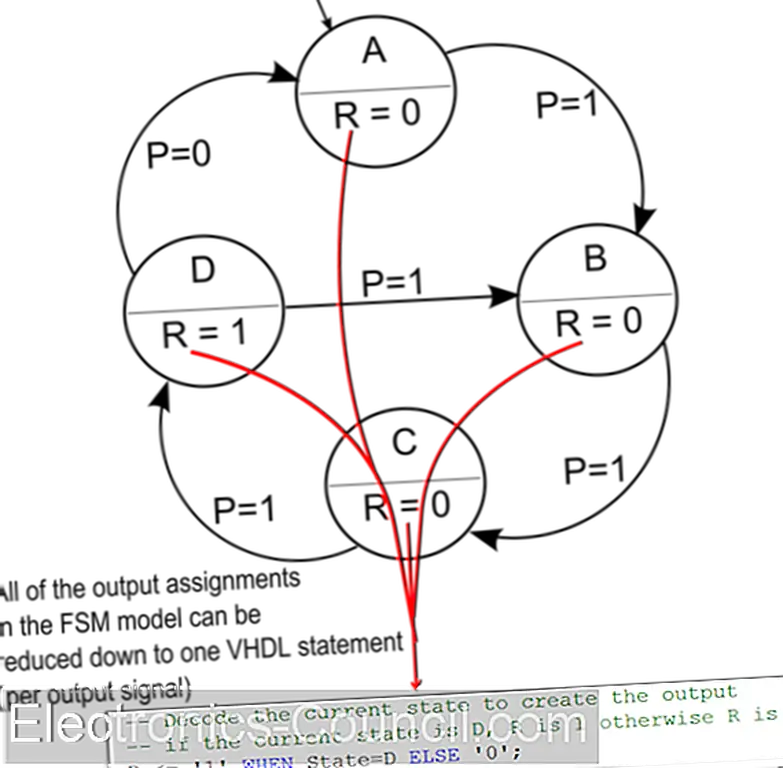

На этих диаграммах приведено краткое описание соотношения между машинной диаграммой конечного состояния и кодом VHDL, необходимым для реализации конечного автомата.

Рисунок 3. Определения состояний в диаграмме FSM и VHDL

Рисунок 4. Правила перехода штата в диаграмму FSM и VHDL

Рисунок 5. Выходы на диаграмме FSM и VHDL

Заключительные слова

В этой статье немного обсуждается природа языков описания аппаратных средств и взаимосвязь между операторами HDL и реализованным оборудованием. Однако основная цель заключалась в том, чтобы показать вам, как писать VHDL для реализации конечного автомата. Процесс включает создание объекта VHDL, определяющего входы и выходы вашего конечного автомата, а затем запись правил переходов состояний в блоке архитектуры VHDL. Используя предоставленный здесь шаблон, вы должны иметь всю необходимую информацию для реализации своего собственного FSM.

Файл SimpleFSM VHDL