Понимание приложений PLL: умножение частоты

В этой статье описано, как схема ФАПЧ может быть использован для получения высокой тактовой частоты опорного сигнала от низкочастотного.

Вспомогательная информация

- То, что точно представляет собой фазовую петлю, в любом случае »// www.allaboutcircuits.com/technical-articles/how-to-simulate-a-phase-locked-loop/" target = "_ blank"> Как имитировать фазу- Закрытая петля

- Понимание переходных процессов с фазовой синхронизацией

- Как оптимизировать переходный отклик цикла с фазовой блокировкой

- Проектирование и имитация оптимизированного цикла с фазовой блокировкой

Как вы можете видеть в списке «Поддержка информации», я уже написал пять статей о циклах с фазовой синхронизацией. Я думаю, что эти статьи содержат подробное введение в дизайн и функциональность PLL, но они, безусловно, отсутствуют в одном отношении: они почти ничего не говорят о том, как PLL фактически используются. Единственное «приложение», которое мы обсуждали до сих пор, - это периодический выходной сигнал, который имеет такую же частоту, что и периодический входной сигнал. Это, однако, не очень впечатляет, поскольку мы можем сделать то же самое с цифровым буфером или последователем напряжения постоянного тока.

Пришло время обсудить реальные PLL-приложения, и мы начнем с частотного умножения, что является естественным и интуитивным расширением способности PLL блокировать входную частоту.

Зачем?

Всегда хорошо знать, почему вы хотите что-то сделать, прежде чем это сделать. В случае умножения частоты на основе PLL мы пытаемся создать выходной сигнал с частотой, равной входной частоте, умноженной на некоторую константу. Это может показаться несколько ненужной задачей - почему бы просто не купить другой компонент осциллятора, который напрямую обеспечивает желаемую частоту? Оказывается, существуют различные ситуации, в которых подход PLL весьма полезен:

- Система, построенная вокруг PLL и низкочастотного кристалла, может снизить стоимость по сравнению с системой, которая просто использует высокочастотный кристалл.

- С PLL коэффициент умножения может быть изменен без каких-либо модификаций оборудования. Таким образом, из одной схемы генератора может генерироваться много разных частот.

- PLL, встроенный в микропроцессор, может генерировать высокочастотный тактовый сигнал прямо там, где это необходимо, тем самым устраняя сложности (я думаю об электромагнитных помехах и возможных отражениях), связанных с отправкой высокочастотных сигналов через следы печатной платы.

- Частотно-блокирующие характеристики PLL позволяют генерировать высококачественный (и высокочастотный) периодический сигнал от низкокачественного осциллятора. Для меня это самое важное соображение, потому что оно является наиболее представительным из основных функций PLL. Я бы не ожидал, что независимый VCO будет генерировать тактовый сигнал с частотой, которая может быть точно контролируемой и очень стабильной с течением времени и температуры. Однако действие блокировки PLL позволяет VCO генерировать точные и стабильные часы: если у вас есть, например, низкочастотный генератор на основе кристаллов с отличной точностью и стабильностью, PLL будет «наследовать» эту производительность при производстве более высокая частота за счет блокировки сигнала на основе кристалла.

Как?

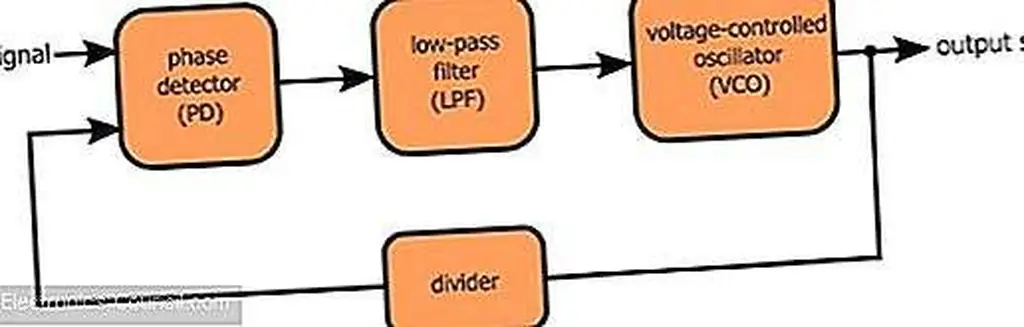

Все, что вам нужно, это делитель:

В частности, вам нужен делитель в контуре обратной связи, так что сигнал, возвращенный обратно к фазовому детектору, имеет частоту, которая ниже частоты выходного сигнала, генерируемого VCO.

Вы можете с некоторым недоумением понять, что разделение частоты сигнала обратной связи приводит к умножению выходного сигнала, но этот метод не является чем-то новым; на самом деле, он полностью аналогичен тому, что мы находим в одной из наиболее широко используемых схем в электронике, а именно на неинвертирующем усилителе на основе op-amp.

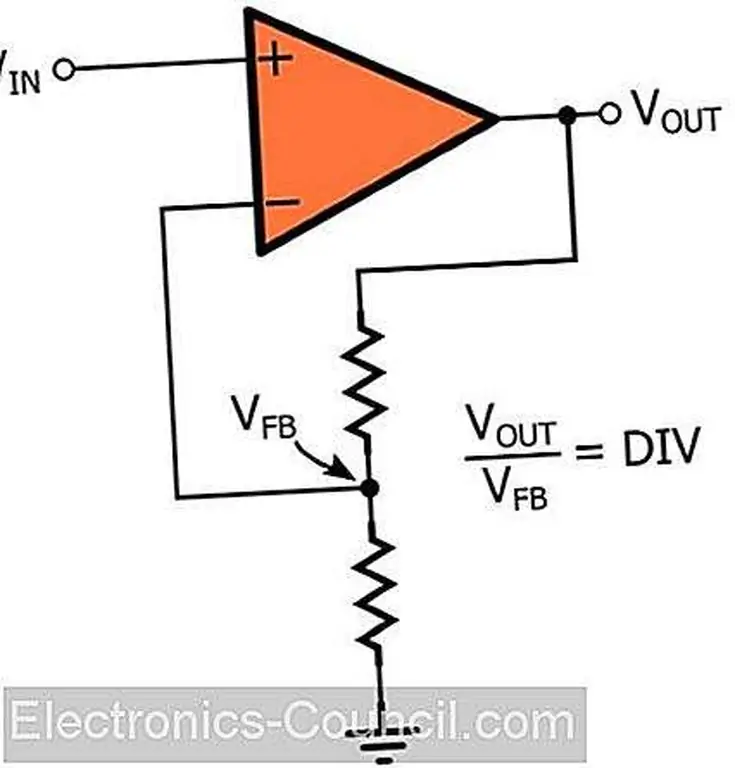

Предположим, у вас есть операционный усилитель, настроенный как последователь напряжения. Выход подключается непосредственно к инвертирующему входному терминалу, и в результате операционный усилитель делает все возможное, чтобы выходное напряжение было равно входному напряжению. Это хорошо и хорошо, но что, если мы хотим получить прибыль? Просто, мы просто используем некоторые резисторы, чтобы превратить петлю обратной связи в делитель напряжения:

Давайте подумаем о том, что мы здесь делаем. Устройство с отрицательной обратной связью заставляет операционный усилитель изменять свой выход с одной целью: сделать напряжение на инвертирующем входе равным напряжению на неинвертирующем входе. Когда он подключен как последователь напряжения, это означает, что V OUT должен равняться V IN.

Но делитель напряжения в контуре обратной связи меняет все. Теперь напряжение на инвертирующем входе меньше DIV, чем напряжение на выходе. Таким образом, чтобы инверторное входное напряжение было равно входному напряжению без напряжения, выходное напряжение должно быть в DIV раз больше входного напряжения.

При использовании ОУ мы создаем усиление напряжения за счет уменьшения амплитуды напряжения обратной связи; с PLL мы создаем частотное усиление за счет уменьшения частоты сигнала обратной связи. Чтобы продолжить аналогию, усиление неинвертирующей схемы ОУ равно коэффициенту, по которому делится напряжение обратной связи, и величина умножения частоты, выполняемая ФАПЧ, равна коэффициенту, по которому частота сигнала обратной связи делится,

Быстрый пример

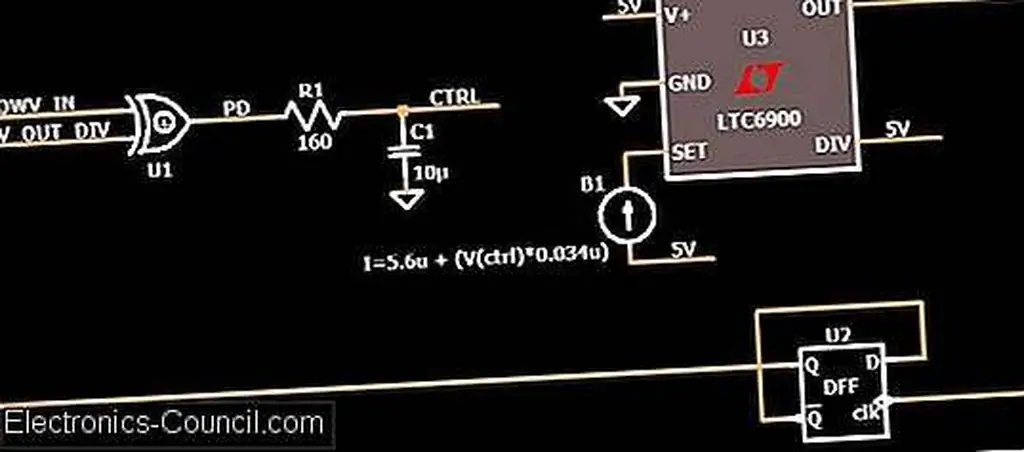

Следующая схема представляет собой LTspice-версию цикла с фазовой автоподстройкой. Вы хорошо знакомы с этой схемой, если прочитали предыдущие статьи. Тем не менее, у этого есть новый компонент: я вставил триггер типа D, подключенный как счетчик «разделить на два», в контур обратной связи.

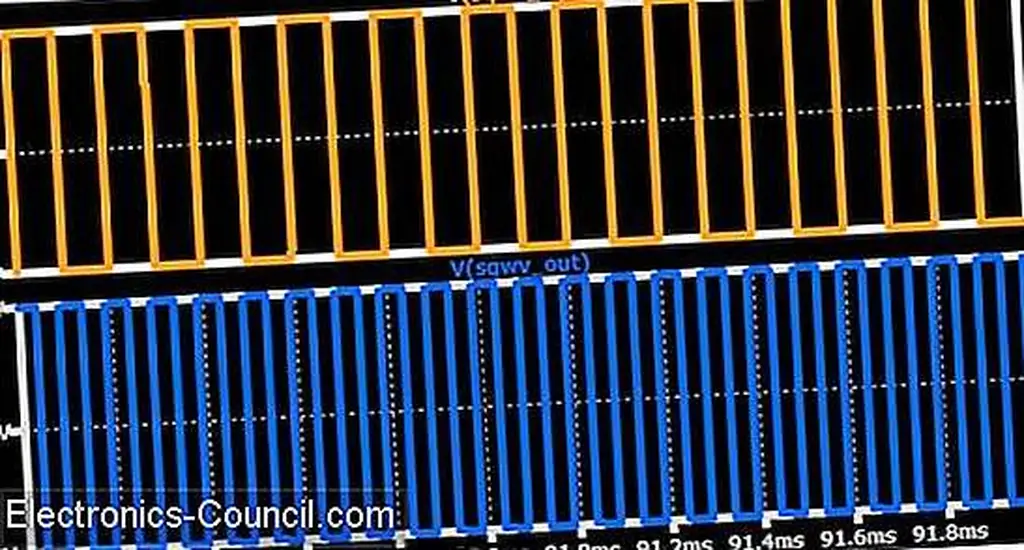

Вот график, который показывает входную форму волны и выходную форму сигнала (после того, как PLL достигло блокировки).

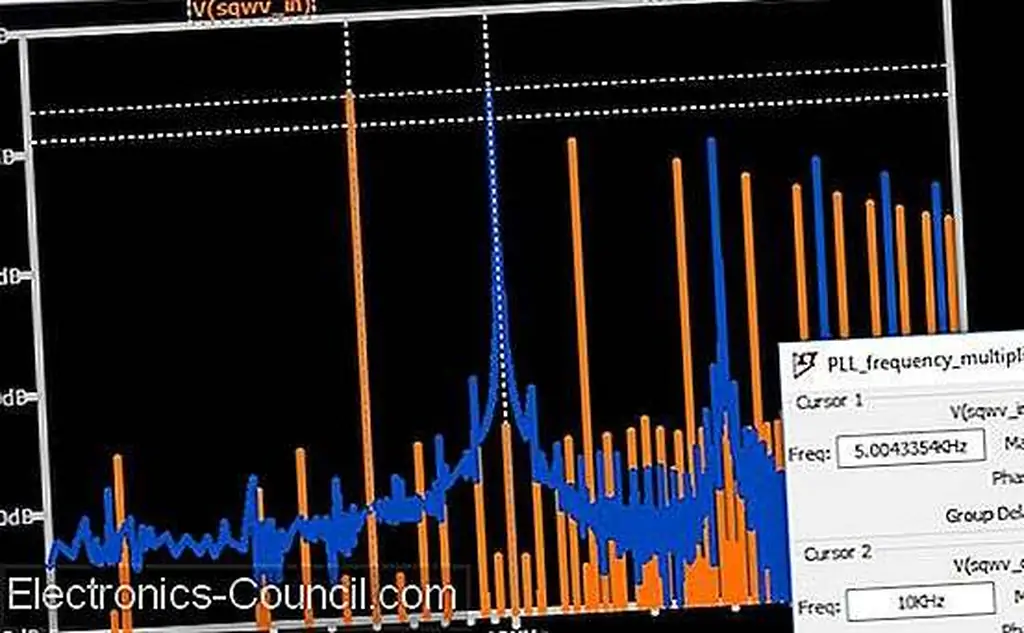

Выходной сигнал и входной сигнал имеют постоянную фазовую зависимость (как и ожидалось в состоянии блокировки), но выходная частота значительно выше входной частоты. Мы ожидаем, что выходная частота будет выше в два раза, и мы можем легко подтвердить, что это так, посмотрев на FFT:

Вывод

После пяти статей, посвященных фундаментальным характеристикам систем с фазовой автоподстройкой, мы ввели чрезвычайно широкое практическое применение PLL. Добавляя делитель частоты в контур обратной связи, мы можем умножить частоту входного сигнала, сохраняя точность и стабильность входного сигнала. В следующей статье мы рассмотрим дополнительные сведения, связанные с умножением частоты ФАПЧ.

Вы можете загрузить мою схему LTspice, нажав на оранжевую кнопку.

Схема LTspice