Понимание регистра последовательной аппроксимации ADC

Регистр последовательной аппроксимации АЦП является обязательным.

Одним из наиболее распространенных аналого-цифровых преобразователей, используемых в приложениях, требующих частоту дискретизации менее 10 MSPS, является АЦП с последовательным приближением. Этот АЦП идеально подходит для приложений, требующих разрешения от 8 до 16 бит. Для получения дополнительной информации о разрешении и частоте дискретизации, пожалуйста, обратитесь к первой в этой серии статей: Расшифровка разрешения и частоты дискретизации. SAR ADC - один из самых интуитивных аналого-цифровых преобразователей для понимания, и как только мы знаем, как работает этот тип АЦП, становится очевидным, где лежат его сильные и слабые стороны.

Основные операции SAR ADC

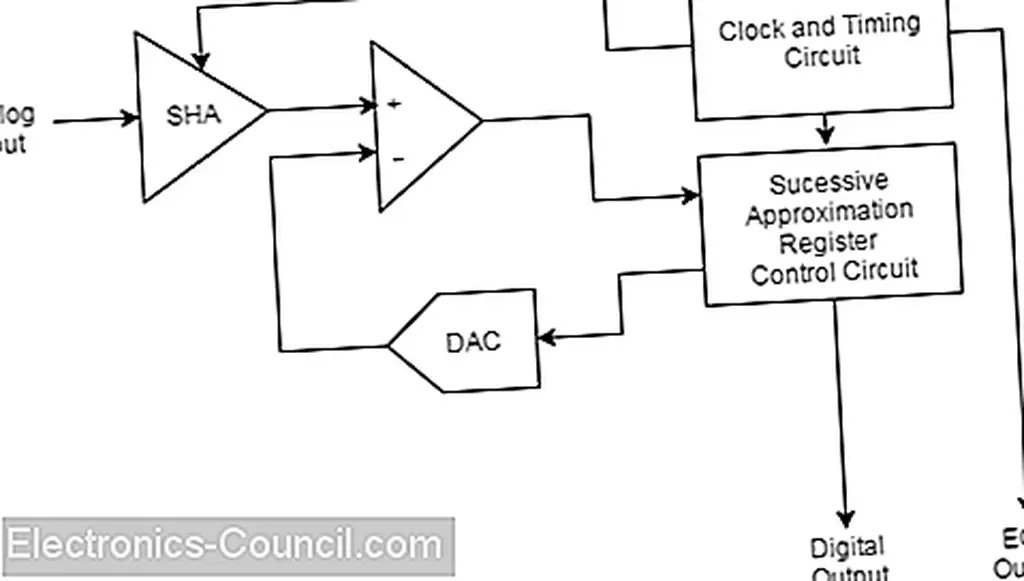

Аналого-цифровой преобразователь базового последовательного приближения показан на схеме ниже:

SAR ADC выполняет следующие действия для каждого образца:

- Аналоговый сигнал отбирается и удерживается.

- Для каждого бита логика SAR выводит двоичный код на ЦАП, который зависит от текущего бита под контролем, и предыдущие биты уже приближаются. Компаратор используется для определения состояния текущего бита.

- После того, как все биты были аппроксимированы, цифровое приближение выводится в конце преобразования (EOC).

Операция SAR лучше всего объясняется как алгоритм бинарного поиска. Рассмотрим приведенный ниже код. В этом коде текущий бит под контролем установлен в 1. Полученный двоичный код из этого выводится в ЦАП. Это сравнивается с аналоговым входом. Если результат выхода ЦАП, вычитаемого из аналогового входа, меньше 0, бит под контролем установлен в 0.

%8−bit digital output is all zeros digital output = zeros(1, 8); %Normalised to one for example reference voltage = 1; for i=1:8 %current output bit set to 1: digital output(i)=1; compare threshold = 0; %Output digital output in current form to DAC: for j=1:i compare threshold = compare threshold+digital output(j)*reference voltage/(2ˆj); end %Comparator compares analog input to DAC output: if (input voltage−compare threshold<0) digital output(i)= 0; end end

Скачать код

Если мы рассмотрим пример аналогового входного значения 0, 425 В и опорный сигнал напряжения 1 В, мы можем приблизить выход 8-разрядного АЦП следующим образом:

- Установите первый бит 8-разрядного вывода на 1, поэтому выход на ЦАП равен 0, 5

- 0, 5, вычитаемый из 0, 425, меньше 0, поэтому установите первый бит вывода на 0

- Установите второй бит 8-разрядного вывода на 1, поэтому выход на ЦАП равен 0, 25

- 0, 25, вычитаемое из 0, 425, больше 1, поэтому второй бит выхода равен 1

- Установите третий бит 8-разрядного вывода на 1, поэтому выход на ЦАП равен 0, 375

- 0, 375, вычитаемое из 0, 425, больше 1, поэтому третий бит - 1

Этот процесс повторяется для всех 8 бит, пока не будет определено, что выход:

01101100

Из этого процесса становится очевидным, что N-разрядный SAR-АЦП должен требовать, чтобы N периодов времени успешно аппроксимировали вывод. В результате этого, хотя эти АЦП имеют низкую мощность и требуют очень мало места, они не подходят для высокоскоростных приложений с высоким разрешением. Поскольку эти АЦП требуют очень мало места, они часто обнаруживаются как периферийные устройства внутри микроконтроллеров или в чрезвычайно небольшой упаковке.

Возможно, немного менее интуитивным является тот факт, что рассеиваемая мощность измеряется с частотой дискретизации. В результате этого эти АЦП идеально подходят для использования в приложениях с малой потребляемой мощностью, где АЦП необходимо принимать образцы нечасто.

В этой архитектуре стоит отметить отсутствие конвейера и связанные с этим задержки. В результате АЦП SAR подходит для мультиплексированных приложений.

Две особенности АЦП, которые определяют общие характеристики АЦП, не удивительно, ЦАП и Компаратор.

Емкостный ЦАП

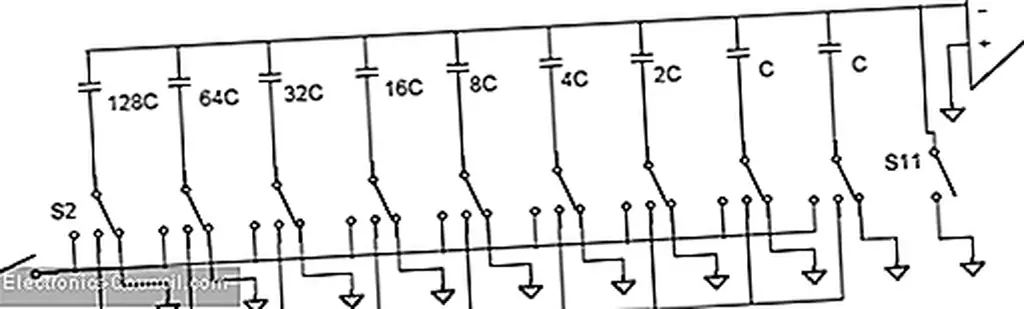

Емкостной ЦАП содержит N конденсаторов для N-разрядного разрешения с добавлением второго наименее значимого разрядного конденсатора. Пример емкостного ЦАП показан ниже:

При получении общий терминал подключается к заземлению, закрывая S11, а аналоговый вход (Ain) заряжает и разряжает конденсаторы. Режим удержания происходит, если вход отключен путем открытия S1. Затем открывается S11, ведущий общий терминал к -Ain. Если S2 затем подключается к Vref, к -Ain добавляется напряжение, равное Vref / 2. Решение о наиболее значительном бит определяется после этого.

Максимальное время установления емкостного ЦАП определяется временем установления наиболее значимого бита. Это связано с тем, что наибольшее изменение в выходе ЦАП происходит из-за этого наиболее значимого бита.

Вы можете быть прощены за то, что считаете, что 16-разрядный SAR-АЦП займет в два раза больше, чтобы получить выход как 8-разрядный SAR-АЦП из-за того, что в два раза больше выходных бит. В действительности, время установления внутреннего ЦАП в 16-разрядном SAR-АЦП займет гораздо больше времени, чем время установления 8-разрядной версии. В результате этого частота дискретизации SAR ADC с высоким разрешением значительно снижается по сравнению с версиями с низким разрешением.

Линейность общего АЦП зависит от линейности внутреннего ЦАП. В результате этого решение АЦП, что неудивительно, ограничено разрешением внутреннего ЦАП.

Компаратор

Компаратор должен быть как точным, так и быстрым. Как и в ЦАП, неудивительно, что компаратор должен иметь разрешение, по крайней мере, столь же хорошее, как и SAR ADC. Шум, связанный с компаратором, должен быть меньше наименее значимого бита АЦП SAR.

Резюме

Сильные стороны АЦП SAR

- Низкое энергопотребление

- Физически маленький

Слабые стороны АЦП SAR

- Низкие частоты дискретизации для высоких разрешений

- Ограниченное разрешение из-за пределов ЦАП и компаратора

- Размер увеличивается с количеством бит

Приложения АЦП SAR

Идеально подходит для многоканальных систем сбора данных с частотой дискретизации до 10 МГц и разрешением от 8 до 16 бит.

Следующая статья в серии: Понимание АДЦ Delta-Sigma