Понимание переходных процессов с фазовой синхронизацией

В этой статье мы будем использовать симуляции SPICE, чтобы внимательно изучить, как петля с фазовой синхронизацией переходит в заблокированное состояние.

До сих пор я написал две статьи о петлях с фазовой синхронизацией (PLL). Первое - это общее введение в петли с фазовой синхронизацией, а вторая - пояснение и пояснение схемы LTspice, которая может использоваться как платформа для экспериментов с PLL.

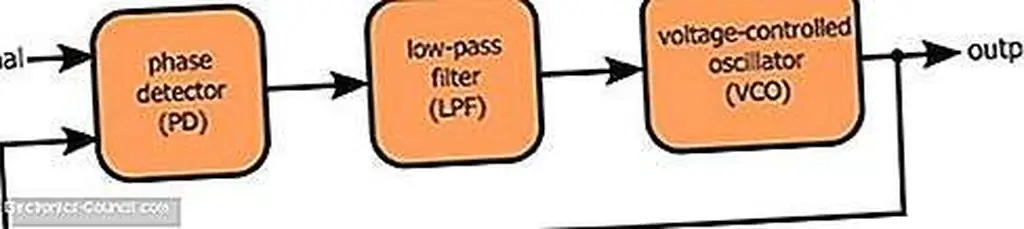

В этой статье мы будем использовать симуляции SPICE для более полного понимания поведения переходных процессов PLL. На всякий случай вам нужно напоминание, вот структура очень простой PLL.

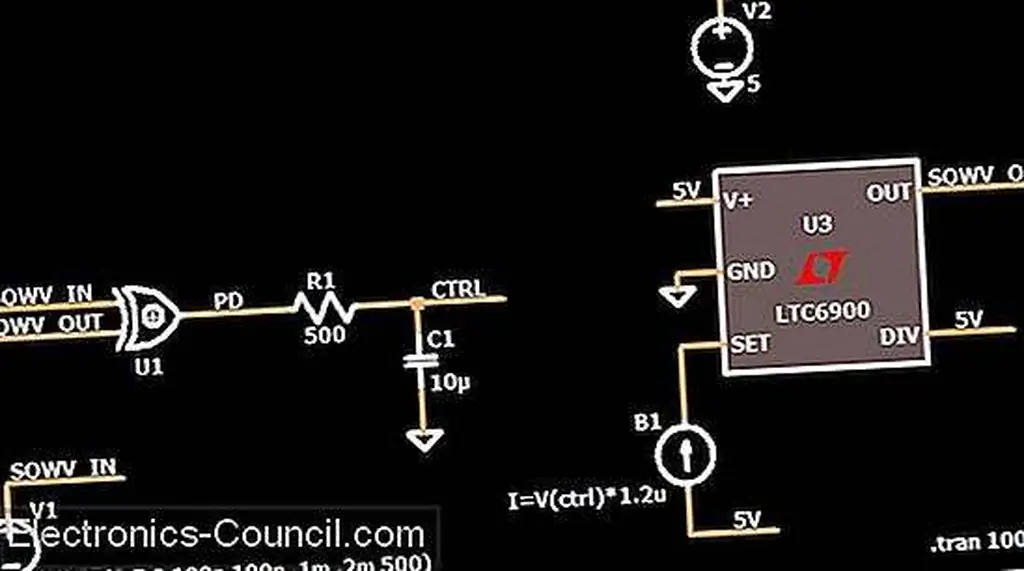

И вот схема LTspice, поэтому вам не нужно нажимать на предыдущую статью.

По моему опыту, системы с отрицательной обратной связью в целом могут быть трудно проанализированы качественно. PLL особенно сложны, и я думаю, что это частично связано с тем, что управляющая переменная трансформируется по мере ее прохождения по контуру.

В неинвертирующей конфигурации ОУ, например, вход представляет собой напряжение, выход представляет собой напряжение, и обратная связь появляется как напряжение на инвертирующем входном терминале операционного усилителя. В PLL ситуация совсем иная. Входная переменная представляет собой фазу (или частоту, в зависимости от вашей перспективы), а переменная обратной связи представляет собой фазу (или частоту), но между этими двумя этапами переменная представляет собой амплитуду напряжения. (Подумав об этом чуть больше, мне интересно, является ли эта характеристика большим препятствием для количественного анализа, чем для качественного анализа).

Другим запутанным аспектом функциональности PLL является туманная взаимосвязь между частотой и фазой. VCO генерирует частоту, но ее частотные вариации используются для установления фазового соотношения, и это фиксированное отношение фаз приводит к одинаковым входным и выходным частотам посредством действия фазового детектора. Два основных момента, которые вам нужно иметь в виду, если вы планируете разгадать эту тайну, следующие:

- Частотные вариации могут использоваться для установления фазового соотношения. Представьте себе случайное изменение частоты одной квадратной волны до тех пор, пока нарастающий фронт не будет совпадать с нарастающим фронтом другой прямоугольной волны. Теперь у вас есть выравнивание по фазе (но выравнивание не будет продолжаться, если частоты будут разными).

- Выход фазового детектора может быть постоянным только тогда, когда входные частоты в точности равны (так как разности частот всегда будут приводить к постепенным изменениям фазового выравнивания двух сигналов). Таким образом, система обратной связи в стиле PLL, которая приводит к выводу выходного сигнала фазового детектора на постоянное значение, заставит выходную частоту быть идентичной входной частоте.

Поиск частоты … и фазы

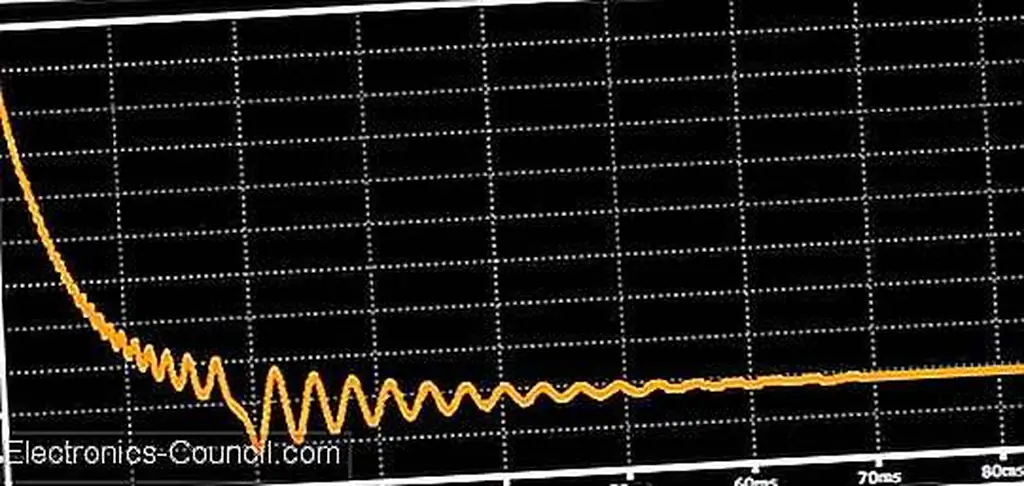

Я закончил предыдущую статью с графиком управляющего напряжения (т. Е. Сигнала фазового детектора с низким пропусканием) в зависимости от времени. Давайте снова посмотрим на этот ответ.

Это очень интересный сюжет, на мой взгляд. Начальные условия приводят к управляющему напряжению, которое начинается с верхнего конца диапазона 0-5 В. Затем напряжение быстро уменьшается до тех пор, пока оно не окажется в общей близости от установившегося значения (~ 2, 36 В). Затем он испытывает некоторые высокоамплитудные колебания, прежде чем начнет оседать на конечном значении.

Этап 1

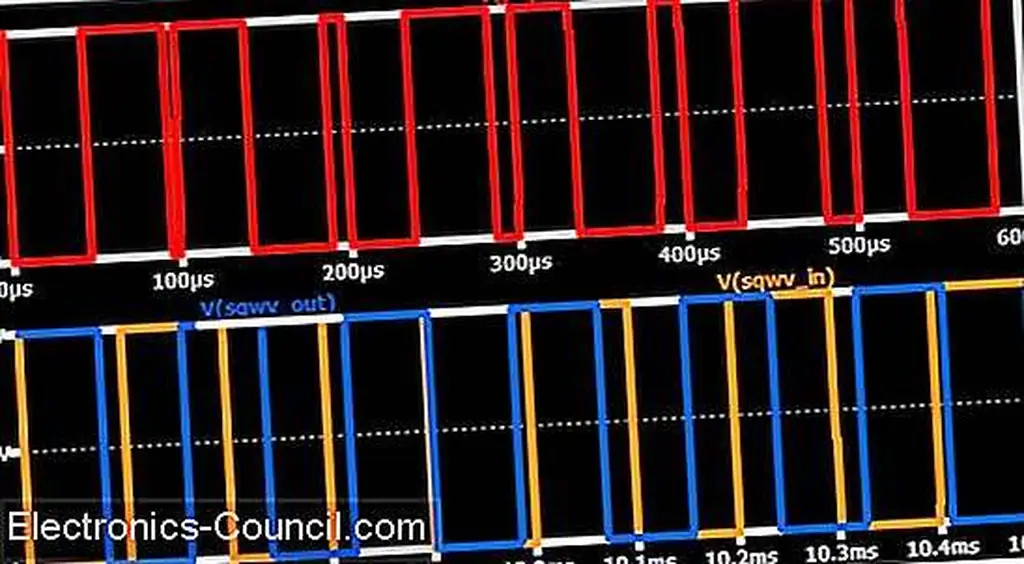

Частоты изначально совершенно разные (как и ожидалось). Выходной сигнал составляет ~ 10, 5 кГц, по сравнению с фиксированной частотой 5 кГц входного сигнала:

Однако, как видно из выхода фазового детектора, эта разность частот не приводит к чему-либо около 100% рабочего цикла.

Следовательно, управляющее напряжение совершает погружение к среднему значению выхода ПД. На этом первом этапе система действительно не ищет стабильное состояние. Это скорее подготовка к фазе поиска.

Этап 2

По знаку 10 мс частоты намного ближе (6 кГц против 5 кГц):

Это меньшее различие в частоте приводит к изменениям низковольтного напряжения управления, которые становятся заметными в течение 10-19 мс участка графика.

Я уверен, что вы уже заметили разрыв, который происходит в ~ 19 мс: есть явное прерывание в закономерности колебаний. Возможно, вы также заметили, что этот разрыв совпадает с первым, когда управляющее напряжение достигает значения, на котором выход будет в конечном итоге оседать (т. Е. После достижения блокировки).

Я точно не знаю, как интерпретировать это событие, но, похоже, он инициирует третий этап переходного отклика: система обнаружила установившееся значение, которое первоначально является смещением по постоянному току колебаний и постепенно становится амплитудой напряжения как колебания отмирают.

Этап 3

Во время этапа 3 управляющее напряжение осциллирует по мере того, как система пытается достичь состояния, в котором 1) входные и выходные частоты идентичны, и 2) установлено правильное соотношение фаз входного сигнала. Помните, что PLL не может достичь устойчивого состояния, пока оба этих условия не будут выполнены. Этот процесс заставляет меня думать о том, что человек вращает частотный регулятор назад и вперед, наблюдая за областью действия, пытаясь достичь и поддерживать указанную фазовую связь, все меньше и меньше вращаясь, так как фазовое отношение стремится оставаться ближе к желаемому значению.

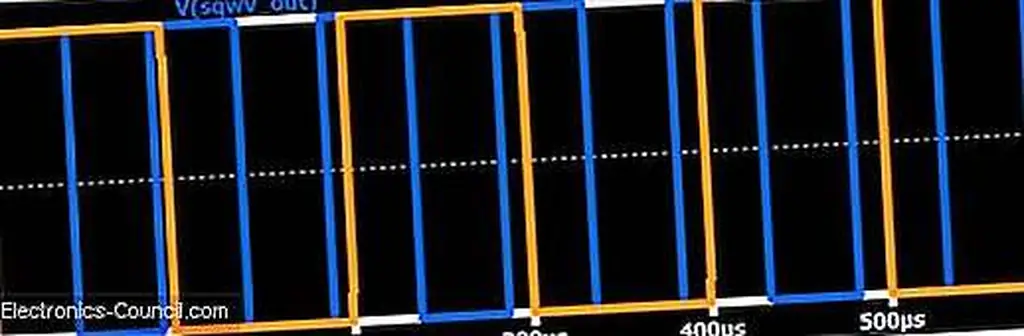

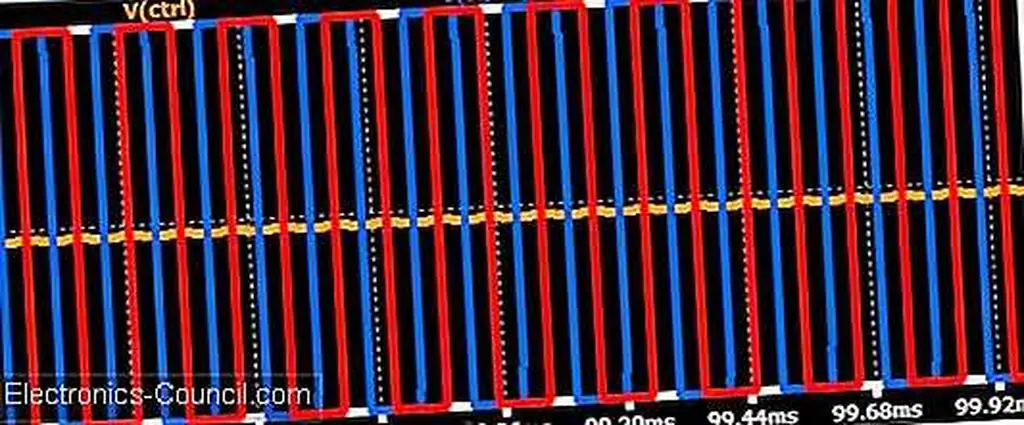

Этот следующий график демонстрирует результат всей этой поисковой и регулировочной и низкочастотной фильтрации и отрицательной обратной обратной связи. Частоты идентичны, а разность фаз - именно то, что фазовый детектор должен производить среднее значение, которое удерживает ГУН на правильной частоте.

Вывод

В этой статье мы использовали симуляции SPICE, чтобы получить представление о процессе, с помощью которого петля с фазовой синхронизацией достигает заблокированного состояния. Интересно видеть, как переходный отклик проявляет те же колебательные поведения, которые мы ожидаем от других типов систем управления, несмотря на то, что PLL сильно отличаются от схем обратной связи, таких как усилители на основе усилителя. В следующей статье мы изменим фильтр нижних частот и посмотрим, как эти изменения влияют на производительность PLL.

Не стесняйтесь загружать мою схему LTspice, нажимая на оранжевую кнопку.

Схема LTspice