Опасности в комбинированной логике

Узнайте о рисках в схемах комбинационных логических схем

Если вход комбинационной схемы изменится, на выходе могут появиться нежелательные изменения переключения. Эти изменения возникают, когда разные пути от входа к выходу имеют разные задержки. Если из ответа на одно изменение входа и для некоторой комбинации задержки распространения выход мгновенно переходит в 0, когда он должен оставаться постоянным значением 1, считается, что схема имеет статическую опасность 1. Аналогично, если выход мгновенно переходит в 1, когда он должен оставаться с постоянным значением 0, считается, что схема имеет 0-опасность.

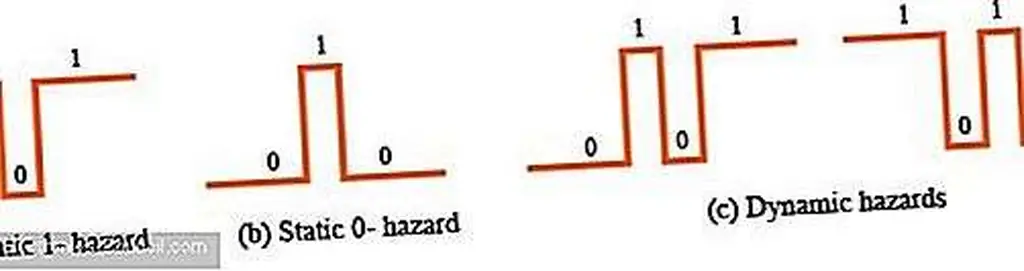

Если выход должен изменить значения от 0 до 1 или от 1 до 0, этот выход может меняться три или более раз; если такая ситуация должна произойти, считается, что схема имеет динамическую опасность. На рисунке 1.1 показаны различные выходы схемы с опасностями. В каждом из трех случаев стабильный выход схемы правилен, однако на выходе схемы при изменении входа появляется изменение переключения.

Рисунок 1.1

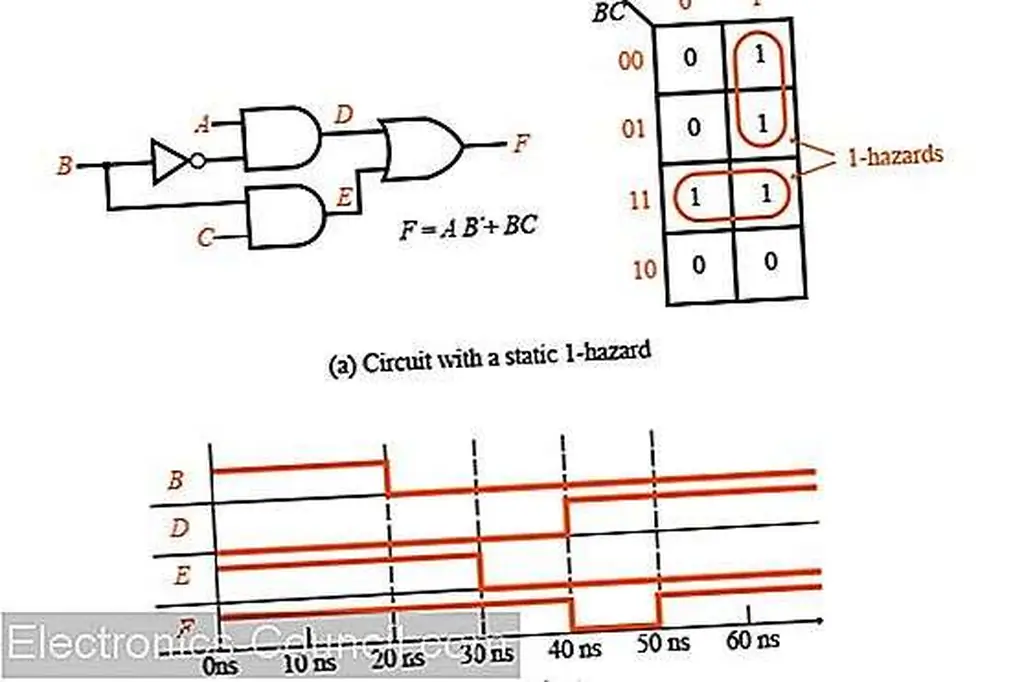

Первая опасность на рис. 1.2, статическая 1-опасность показывает, что если A = C = 1, то F = B + B '= 1, поэтому выход F должен оставаться с константой 1, когда B изменяется от 1 до 0. Однако на следующей иллюстрации статическая О-опасность, если каждый затвор имеет распространение 10 нс, E будет идти до 0 до того, как D перейдет к 1, в результате чего на выходе F появится кратковременное значение 0. Это также известно как сбой вызванных 1-опасностью. Следует отметить, что сразу после того, как B изменится на 0, как вход инвертора (B), так и выход (B ') равны 0 до истечения времени задержки. В течение этого периода распространения оба этих входных члена в уравнении для F имеют значение 0, поэтому F также мгновенно переходит в значение 0.

Эти опасности, статические и динамические, полностью не зависят от задержек распространения, существующих в цепи. Если комбинационная схема не имеет опасности, то говорят, что для любой комбинации задержек распространения и для любого индивидуального изменения ввода этот вывод не будет иметь изменения в значении ввода-вывода. Напротив, если цепь должна была содержать опасность, тогда будет некоторая комбинация задержек, а также изменение входа, для которого выход в цепи содержит переходный режим.

Такая комбинация задержек, которые приводят к сбою, может или не может произойти при реализации схемы. В некоторых случаях очень маловероятно, что такие задержки произойдут. Переходные процессы (или сбои), возникающие из-за статических и динамических факторов времени, очень редко вызывают проблемы в полностью синхронных цепях, но они являются серьезной проблемой в асинхронных схемах (которая включает номинально синхронные схемы, которые включают либо использование асинхронных предустановленных / сбросных входов, которые используйте встроенные часы).

Изменение входа и выхода также зависит от того, как каждый вентиль будет реагировать на изменение входного значения. В некоторых случаях, если в течение короткого промежутка времени изменяется несколько входных ворот, затвор может или не может реагировать на отдельные изменения ввода. Один пример на рисунке 1.2, предполагая, что инвертор (B) имеет задержку распространения 2ns вместо 10ns. Затем входные изменения D и E, достигающие выходного логического элемента ИЛИ, равны 2ns друг от друга, поэтому логический элемент ИЛИ может или не может сгенерировать ошибку 0.

Рисунок 1.2

Говорят, что ворота, отображающие этот тип ответа, имеют так называемую инерционную задержку. Предполагается, что часто инерциальная величина задержки совпадает с задержкой распространения затвора. Когда это произойдет, вышеприведенная схема ответит с ошибкой 0 только на задержку распространения инвертора, которая больше 10 нс. Однако, если входной вентиль неизменно реагирует на изменение ввода, которое имеет задержку распространения, считается, что он имеет идеальную или задержку транспортировки. Если логический элемент ИЛИ, показанный выше, имеет такой тип задержки, то при любом ненулевом значении задержки распространения инвертора генерируется сбой.

Опасности всегда можно обнаружить с помощью карты Карно. Карта, показанная выше на рисунке 1.2, которая не представляет собой ни одного цикла, охватывает как minterms ABC, так и AB'C. Таким образом, если значение A = C = 1 и значение B, оба этих термина могут мгновенно перейти на 0; от этого мгновенного изменения в F обнаружен сбой. Чтобы обнаружить опасности в двухуровневой комбинационной схеме AND-OR, выполняется следующая процедура:

Выражение суммы продукции для схемы должно быть выписано.

Каждый термин должен быть нанесен на карту и, если возможно, зациклен.

Если любые два соседних 1 не охвачены одним и тем же циклом, тогда существует 1-опасность для перехода между этими двумя 1. Для любой n-переменной карты этот переход происходит только тогда, когда одна переменная меняет значение, а остальные n 1-переменные сохраняются постоянными.

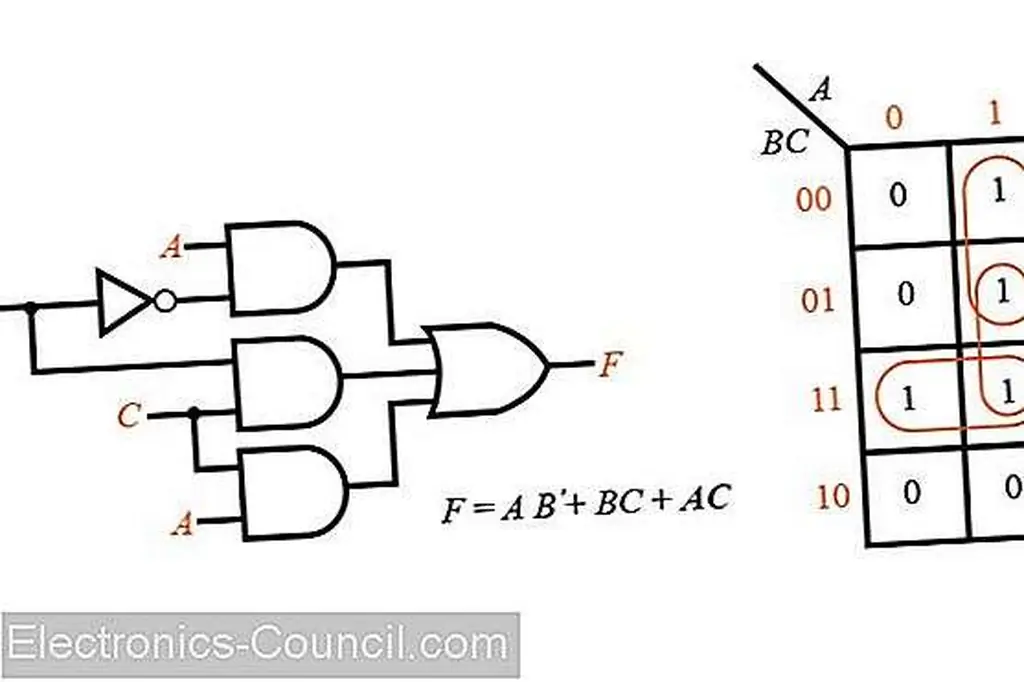

Если к карте Карно на рисунке 1.2 (а) добавить еще один цикл, а затем добавить соответствующий затвор в схему на рисунке 1.3 ниже, опасность может быть устранена. Термин AC остается постоянным значением 1, а B меняется, поэтому глюк не может появиться на выходе. С этим изменением F больше не является минимальным SOP.

Рисунок 1.3

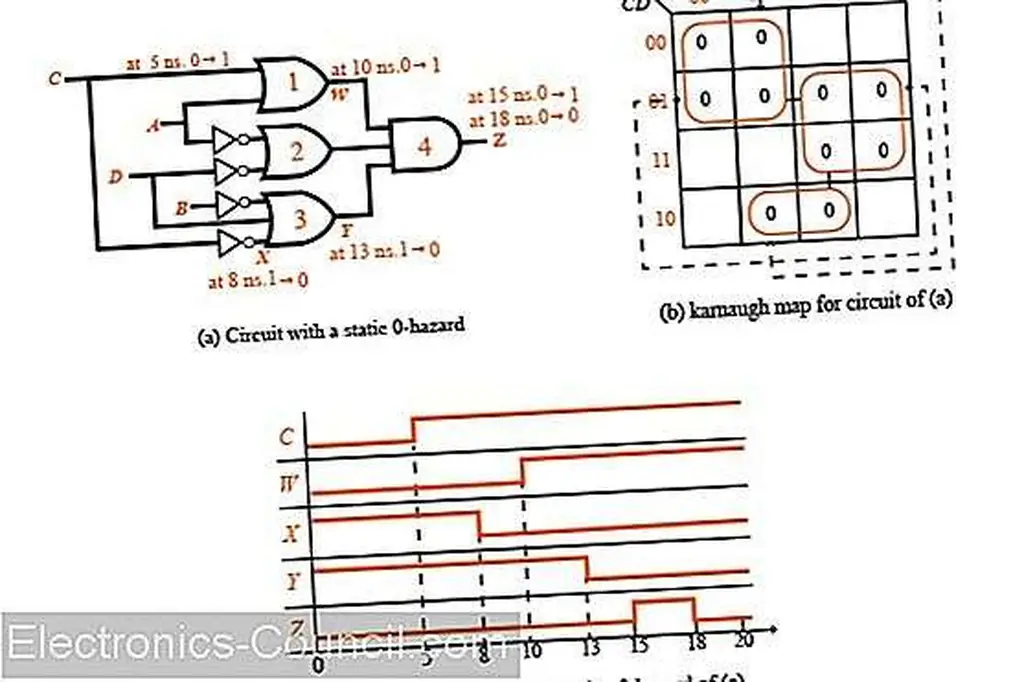

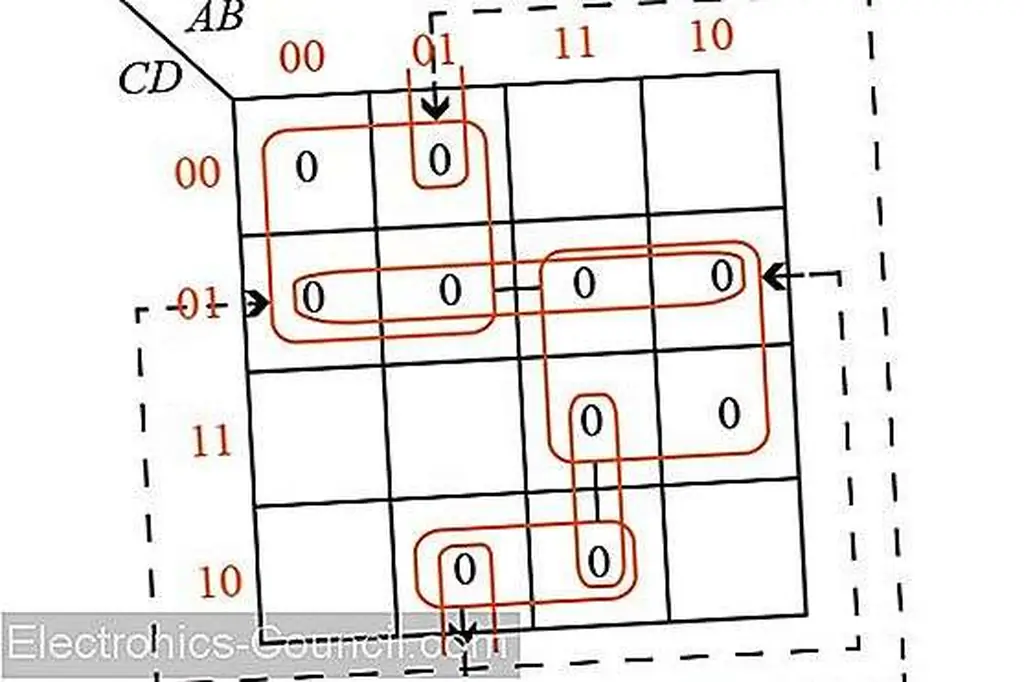

Рисунок 1.4 (a) представляет собой схему с многочисленными 0-опасностями. Функция, которая представляет выход схемы:

F = (A + C) (A '+ D') (B '+ C' + D)

Карта Карно на рисунке 1.4 (b) имеет четыре пары смежных 0, которые не охватываются общей петлей. Стрелки указывают, где каждый 0 не зацикливается, и каждый из них соответствует 0-опасности. Если A = 0, B = 1, D = 0, а C изменяется от 0 до 1, существует вероятность появления всплеска на выходе для любой комбинации задержек ворот. наконец, на рисунке 1.4 (с) изображена временная диаграмма, которая предполагает задержку 3 нс для каждого отдельного инвертора и задержку 5 нс для каждого логического элемента И и каждого логического элемента ИЛИ.

Рисунок 1.4

0-опасности могут быть устранены путем циклизации дополнительных первичных импликантов, которые перекрывают соседние 0, если они еще не покрыты общей петлей. Исключая алгебраически избыточные термины или консенсусные термины, схему можно свести к следующему уравнению ниже. Использование трех дополнительных циклов полностью устранит 0-опасности, в результате получим следующее уравнение:

F = (A + C) (A '+ D') (B '+ C' + D) (C + D ') (A + B' + D) (A '+ B' + C ')

Этот рисунок ниже иллюстрирует карту Карно после удаления 0-опасных факторов.

Рисунок 1.5

Тестирование логических схем

Существенным компонентом проектирования логических схем является то, что окончательная конструкция правильная и, при необходимости, исправление. Чтобы протестировать схему, можно либо построить их, либо имитировать их на цифровом компьютере. Компьютерное моделирование, как правило, быстрее и экономичнее, потому что вам не нужно тратить деньги на компоненты. По мере того как сложность схемы увеличивается, очень важно имитировать дизайн до его фактического построения. Когда конструкция построена в форме интегральной схемы, важно моделировать, потому что изготовление интегральной схемы может занять очень много времени, а исправление ошибок может быть дорогостоящим исправлением. Моделирование выполняется до фактической сборки по многим причинам: подтверждение правильности конструкции логически, обеспечение правильности выбора времени всех логических сигналов и проверка неисправных компонентов схемы в качестве помощи в поиске тестов для схемы.

Для моделирования схемы логических схем необходимы специальные программы для создания дизайна на компьютере. Во-первых, необходимо указать любые компоненты и подключиться к логическим входам и выходам. После этого эти входы могут быть указаны. Наконец, выходные сигналы схемы должны быть пересмотрены, чтобы исправить любые ошибки. Конкретное описание схемы может быть введено в программу компьютерного моделирования в отношении списка любых соединений между логическими элементами или может быть в виде нарисованной логической схемы на экране компьютера.

Простая программа компьютерного моделирования для набора комбинационной логики может выглядеть так:

Входы схемы реализованы в первом наборе затворов в цепи, и затем вычисляются выходные значения этих затворов.

Эти выходы, которые были изменены на первом этапе, затем подаются на следующий уровень (или набор) входов затвора. Если какой-либо вход изменился, то вычисляется то же значение ввода.

Предыдущий шаг повторяется до тех пор, пока не будет произведено ни одного изменения входных значений затвора. Когда это выполняется, считается, что схема находится в стационарном состоянии, и, наконец, выходные значения могут быть считаны.

Шаги 1-3 повторяются каждый раз, когда происходит изменение ввода.

Прибытие

На данный момент у вас должно быть понимание статических 0- и 1-опасных факторов и динамических опасностей. Кроме того, если приведена комбинационная схема, вы должны быть в состоянии найти опасности (как 0, так и 1-). Основное понимание должно быть известно о тестировании и моделировании интегральных логических схем.