Потребность в знаниях о технологии гибридных кубиков Micron

С увеличением спроса на высокую пропускную способность памяти в таких областях, как Digital Signal Processing и ASIC Prototyping, решение памяти с высокоскоростным шлюзом данных может быть ответом, которого мы так долго ждали.

Гибридный куб памяти (HMC) - это новейшее устройство памяти, обладающее совершенно новой категорией высокопроизводительной памяти и обеспечивающей беспрецедентную производительность и пропускную способность системы. Конструкция HMC от Micron сочетает в себе передовые логические и DRAM-уровни в один оптимизированный 3D-пакет, который использует технологию сквозного кремния через (TSV). Высокая плотность HMC позволит создавать сети следующего поколения. HMC также будет способствовать снижению энергопотребления в суперкомпьютерных и информационных центрах.

Микрофон HMC-15G-SR Micron

Проблема латентности в устройствах памяти, также известная как классическая «стена памяти», всегда рассматривалась как непреодолимая проблема. Со временем пропускная способность существующих модулей DRAM имеет узкую системную производительность в мире высокопроизводительных вычислений. HMC - долгожданное решение этих проблем с обычной памятью. Высокие уровни производительности HMC сыграли важную роль в разрыве стены памяти, обеспечении очень высокой пропускной способности и внедрении энергосберегающей системы памяти.

Теория Операции

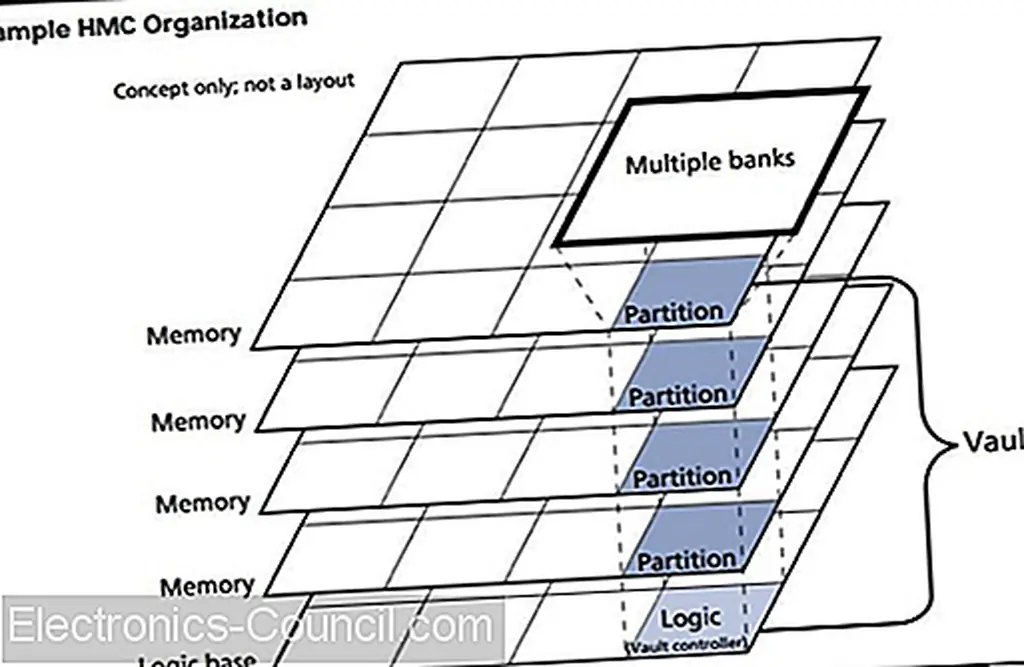

HMC построен путем создания стека гетерогенной матрицы. Различная логика приложения сочетается со стандартным строительным блоком DRAM. Каждый из уровней DRAM 1 ГБ, используемых в стеке, оптимизирован для параллелизма и высокой пропускной способности. Память организована в функционально и оперативно независимые хранилища. Каждое хранилище содержит свой собственный контроллер памяти, также называемый контроллером хранилища. Контроллер хранилища отвечает за управление всеми операциями ссылки на память в этом хранилище.

Стек гетерогенной матрицы

В устройстве используются межсоединения медных столбиков с точной смолой. Логическая матрица использует несколько высокопроизводительных транзисторов для последовательности, обновления, маршрутизации данных, коррекции ошибок и высокоскоростных межсоединений для хоста. Использование TSV позволяет тысячам соединений в вертикальном направлении (направление Z).

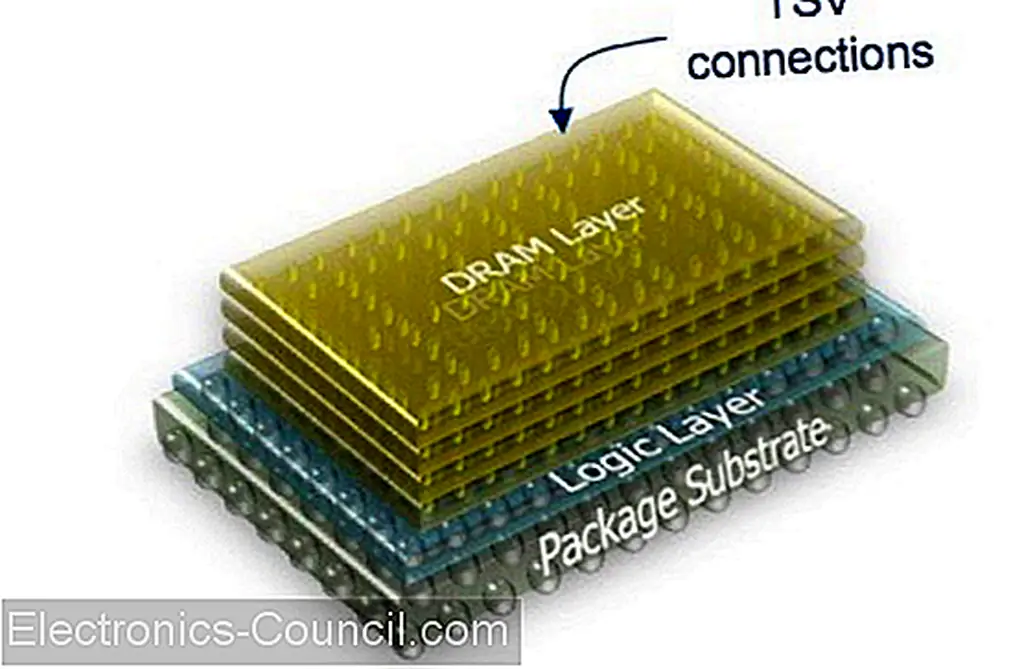

Диаграмма, показывающая медный соединитель с мелким шагом

Благодаря коротким межсоединениям TSV, высокой плотности межсоединений и малой занимаемой площади, он является важным элементом как для трехмерной интеграции на уровне пластины, так и для интеграции на основе упаковки. Использование TSV обеспечивает более низкую задержку, низкую мощность и превосходные электрические характеристики.

Диаграмма, показывающая различные уровни и TSV-соединения

Производительность устройства

Использование сквозных переходных отверстий значительно уменьшает потребность в данных о расстоянии, что приводит к повышению мощности. Было протестировано, что устройство HMC использует на 70% меньше энергии на бит, чем существующие памяти, такие как DDR2 и DDR3. В технологии HMC контроллеру памяти хоста больше не нужно выполнять операции обновления, так как он контролируется контроллером хранилища.

Гибридный куб памяти Micron имеет несколько преимуществ при использовании модуля DDR3: HMC обеспечивает пропускную способность модуля DDR3 в 15 раз и потребляет до 70% меньше энергии на бит, чем существующую память. Технология HMC имела феноменальный успех в снижении объема памяти. Это занимает на 90% меньше места по сравнению с другими используемыми RDIMM. Поскольку он обладает гибкостью логического уровня, он может быть адаптирован к нескольким платформам, что увеличивает объем приложений HMC. Массивный параллелизм HMC доказал свою эффективность в снижении системной задержки. Его функции RAS позволяют встроенные функции проверки и исправления ошибок, что делает HMC более устойчивой системой памяти по сравнению с модулями DDR3.

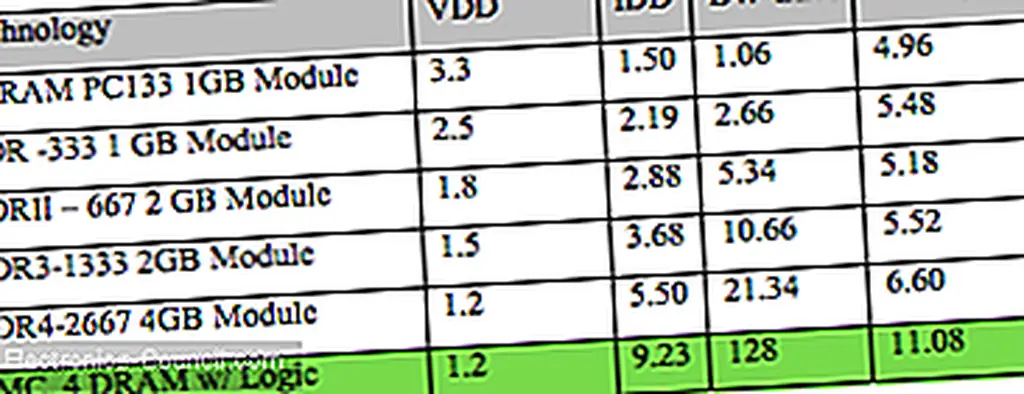

Вот прямое сравнение HMC и DRAM на основе взаимодействия с памятью:

| Нет. | Динамическая память произвольного доступа (DRAM) | Гибридный куб памяти (HMC) |

|---|---|---|

| 1 | Прямое подключение многоядерного процессора к DRAM-специфическим шинам | Прямое подключение к логическому чипу HMC с помощью абстрактного высокоскоростного интерфейса |

| 2 | Сложный планировщик, глубокие очереди, большое переупорядочение, особенно пишет | Нет необходимости в сложном планировщике, просто худшем арбитре, мелкой очереди |

| 3 | Результат - консервативный, эволюционный, некреативный, медленный рост производительности | Гибкость логического слоя позволяет создавать кубы HMC для нескольких платформ и приложений без изменения DRAM большого объема. |

Сравнение технологий 1-го поколения HMC с доступными модулями DDR

рынок

Micron начала поставки HMC в конце сентября 2014 года. Некоторые из основных развивающихся членов, а также клиенты HMC Micron - Altera, ARM, IBM, Open-Silicon Inc., Samsung Electronics Co., Semtech, SK Hynix и Xilinx, Наряду с этими восемью лидерами отрасли существует более 150 дополнительных организаций, преследующих статус усыновителя. Micron пока не раскрывает цену, но утверждает, что повышенная плотность гибридного кубика памяти на бит и уменьшенный форм-фактор снижают общую стоимость владения, позволяя увеличить объем памяти на каждом компьютере и используя на 90% меньше места по сравнению с используемыми в настоящее время RDIMM в индустрия. Слишком рано говорить, действительно ли это будет необходимый seachange, но ранние перспективы кажутся многообещающими.