Рамка OpenCL решает проблемы гетерогенных вычислений

Гетерогенные вычисления относятся к растущему классу систем, в которых приложение выполняется на смеси разнородных процессоров и ускорительных устройств, чтобы максимизировать пропускную способность. Для выполнения программы в этом виде системы требуется парадигма программирования, которая представляет собой последовательное представление системы разработчику приложения. Рамка OpenCL является отраслевым стандартом, созданным для удовлетворения потребностей и проблем гетерогенных вычислительных систем.

На своем самом фундаментальном уровне инфраструктура OpenCL предоставляет программистам приложений агностическое определение платформы разработчика устройства и единую модель памяти для всех устройств, реализующих стандарт. Эти характеристики позволяют программисту OpenCL сосредоточиться на основных задачах разрабатываемого приложения, а не на конкретных деталях конкретного вычислительного устройства.

Первым компонентом среды OpenCL является платформа, которая определяет ресурсы, доступные для выполнения программы. На платформе OpenCL всегда есть хост-процессор и, по крайней мере, одно устройство ускорения. Хост-процессор отвечает за отправку заданий на ускоритель, а также за запуск передачи памяти хоста / ускорителя. Этот хост всегда реализуется с использованием процессора, а ускорителем может быть процессор, графический процессор или FPGA. Управление этими устройствами ускорения осуществляется через общий набор функций API, которые являются частью стандарта OpenCL.

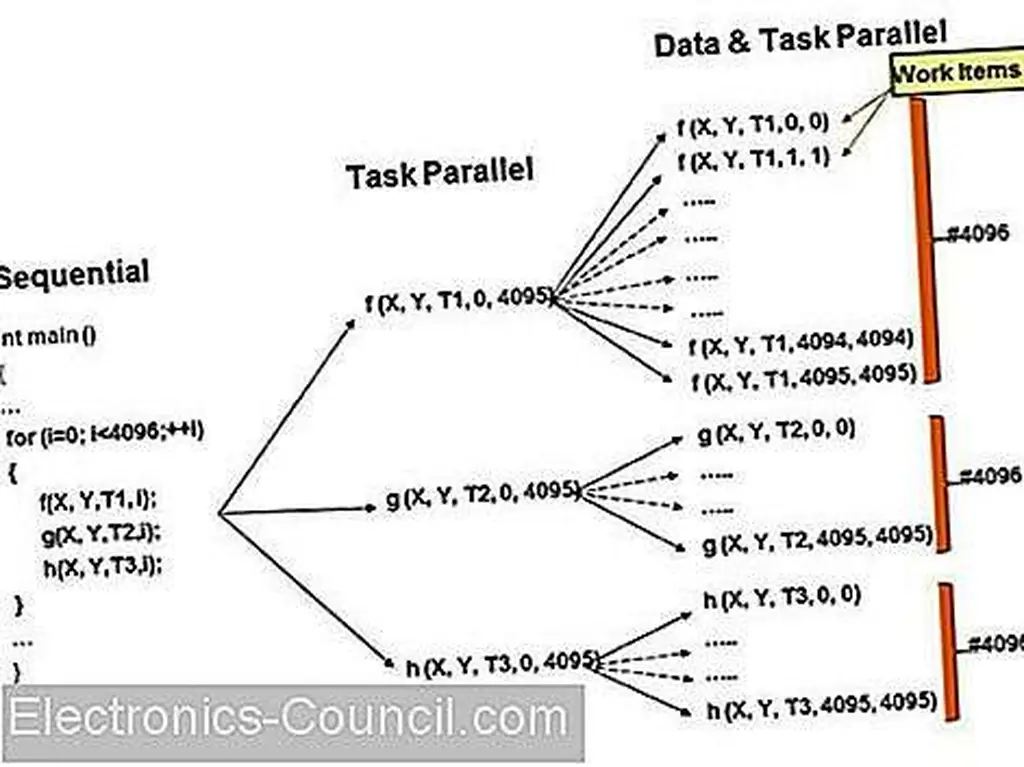

Задания на устройстве ускорения принимают форму выполнения ядра. Ядром является вычислительная функция приложения, работающего на устройстве ускорения. Приложение в OpenCL может иметь одно или несколько ядер, и каждое ядро характеризуется выражением параллельной операции с данными. Например, на рисунке 1 показано преобразование программы, выполняемой на ЦП, в параллельное представление данных и задачи, которое подходит для OpenCL.

Рисунок 1: От последовательного к параллельному приложению sata и задачи

В последовательной версии кода на рисунке 1 функции f, g и h выполняются внутри цикла «for». Каждая функция принимает наборы данных X и Y в качестве входных источников и производит выход T, который не потребляется никакой другой функцией внутри цикла «для». Поэтому цикл в последовательной версии кода может быть распределен по функциям f, g и h для создания параллельного представления задачи приложения, как показано центральным столбцом на рисунке 1. Если каждый вызов функции f, g и h не зависит от предыдущего и следующего вызова, тогда приложение является одновременно задачей и данными, как показано правым столбцом на рисунке 1. Каждый вызов функции f, g или h представляет собой рабочий элемент, выполняемый устройством ускорения. В зависимости от доступных вычислительных ресурсов ускоритель может выполнять все рабочие элементы параллельно или последовательно.

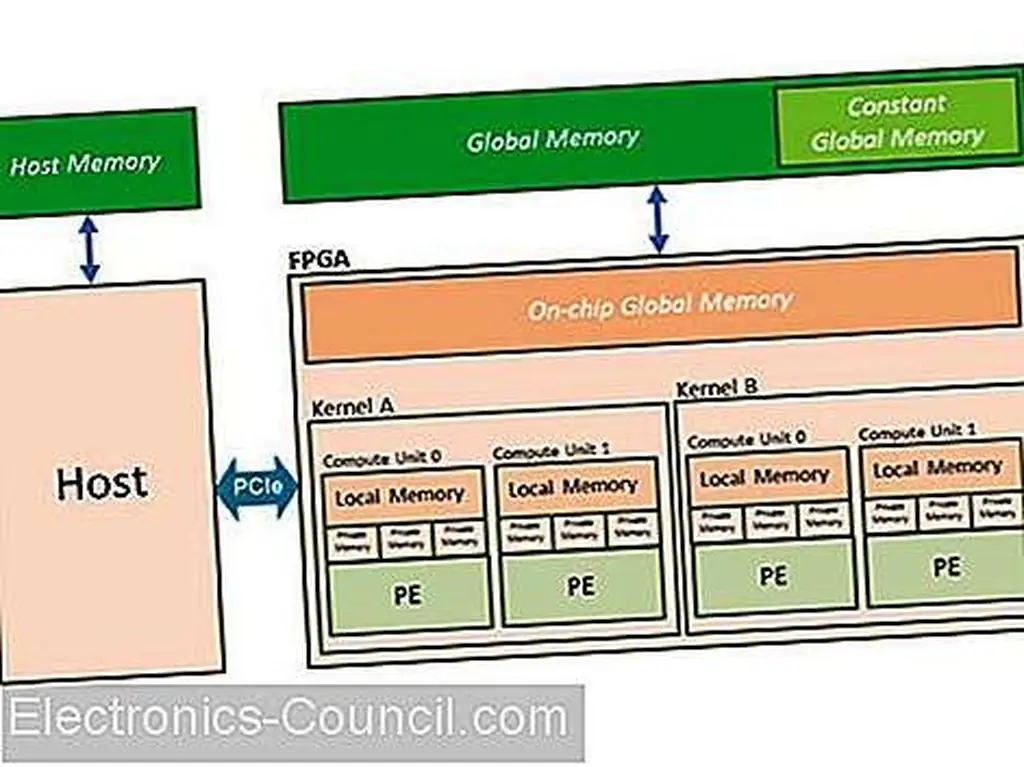

Помимо представления прикладного программиста с моделью параллельного программирования данных агностического устройства, OpenCL предоставляет унифицированную иерархию модели памяти, как показано на рисунке 2.

Рисунок 2: Модель памяти OpenCL

На уровне приложения модели пространство памяти разделяется на память хоста и память устройства. Память, связанная с устройством, далее делится на три уровня иерархии, включая глобальную память, локальную память и частную память. Глобальная память создается из компонентов памяти, подключенных к устройству, таких как SDRAM. Управление буферами, сопоставленными с глобальной памятью, обрабатывается приложением приложения хоста с использованием функций OpenCL API. Функции OpenCL API используются для определения размера буфера, а также для чтения записи в буфер. Из всех типов памяти, поддерживаемых моделью памяти OpenCL, важно иметь в виду, что глобальная память - это память с наибольшей емкостью и самой длинной задержкой, тем самым определяя максимально достижимую пропускную способность данных и являющуюся единственной памятью, которая видна как с хост и устройство.

OpenCL и FPGA

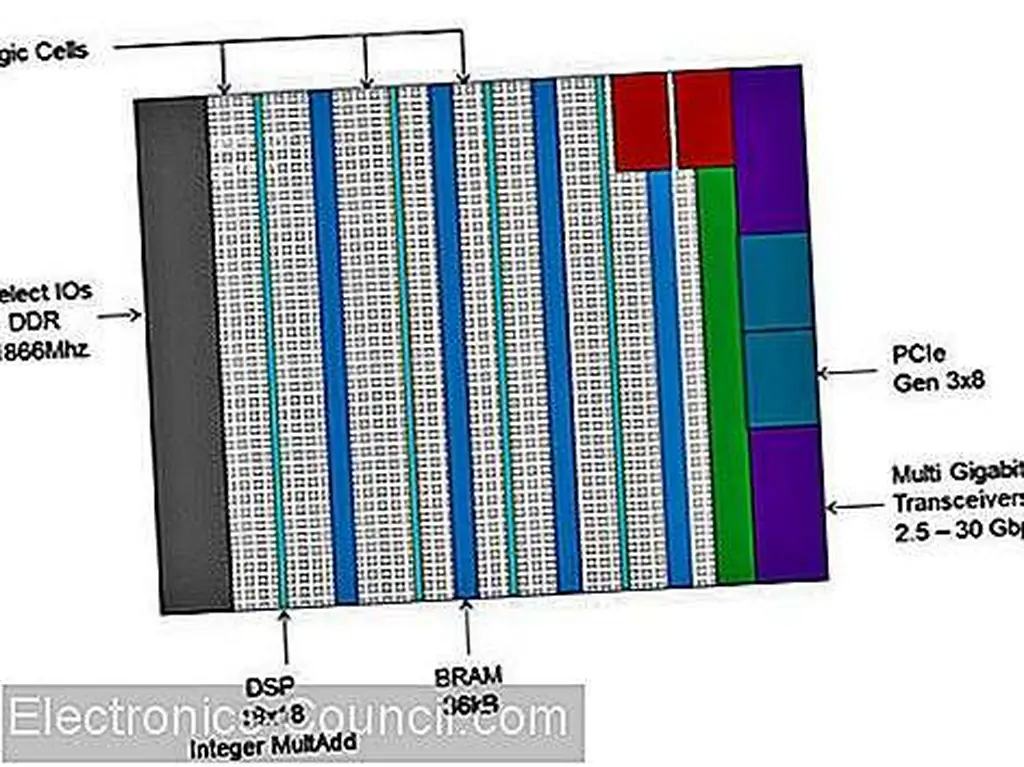

FPGA может быть запрограммирован для разных алгоритмов после изготовления, и, как показано на рисунке 3, имеет таблицы поиска (LUT) для выполнения логических операций, триггеры (FF) для хранения результата LUT и соединения между элементами и ввода-вывода для получения данных в IC и из них. Современные архитектуры FPGA включают в себя дополнительные вычислительные (DSP), хранилища данных (BRAM), высокоскоростные последовательные приемопередатчики и блоки памяти контроллера вне кристалла. Комбинация этих элементов обеспечивает FPGA гибкость для реализации пользовательской логики для заданной рабочей нагрузки.

Рисунок 3: Базовая структура FPGA

В контексте OpenCL ткани FPGA хорошо подходят для такого вида рабочей нагрузки из-за параллельности данных кода ядра. В отличие от других устройств, способных выполнять ядра OpenCL, FPGA-ткань может быть настроена с ядрами, которые полностью оптимизированы для конкретного ядра, что позволяет параллелизму для выполнения ядра масштабироваться с размером FPGA-устройства.

Ядра приложений OpenCL выполняются на вычислительных единицах ускорителя. Единица вычисления относится к ядру процессора или логике ускорителя, которая выполняет операции в функции ядра.

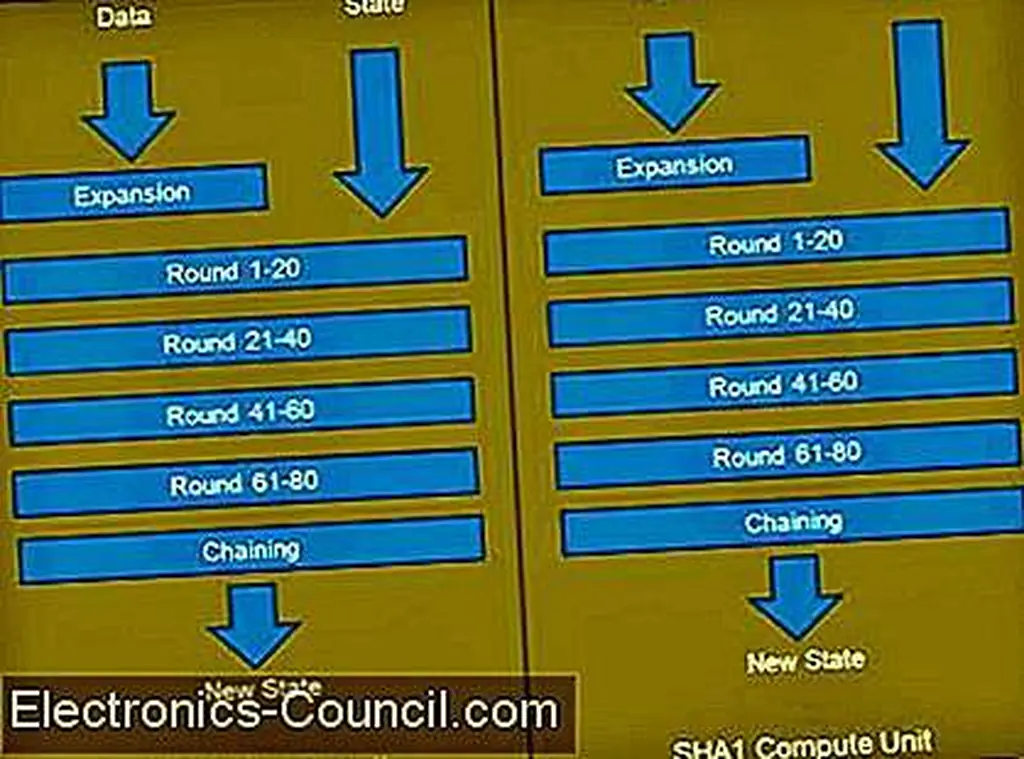

Алгоритм SHA-1

Алгоритм SHA-1 является одним из наиболее часто используемых криптографических хеш-функций. Возможность гарантировать и проверять целостность данных с использованием этих функций послужила основой для онлайн-подписей и безопасного уровня сокетов (SSL), который находится в центре решений для электронной коммерции. Эта функция идеально подходит для FPGA, поскольку она состоит из операций xor, rotation, add и or shift с набором данных из 512 бит на 80 раундов обработки. 512-битная загрузка данных, которая используется в каждом раунде вычисления, может быть вычислена либо параллельным, либо блочным способом.

Рисунок 4: Единица вычисления FPGA для SHA-1

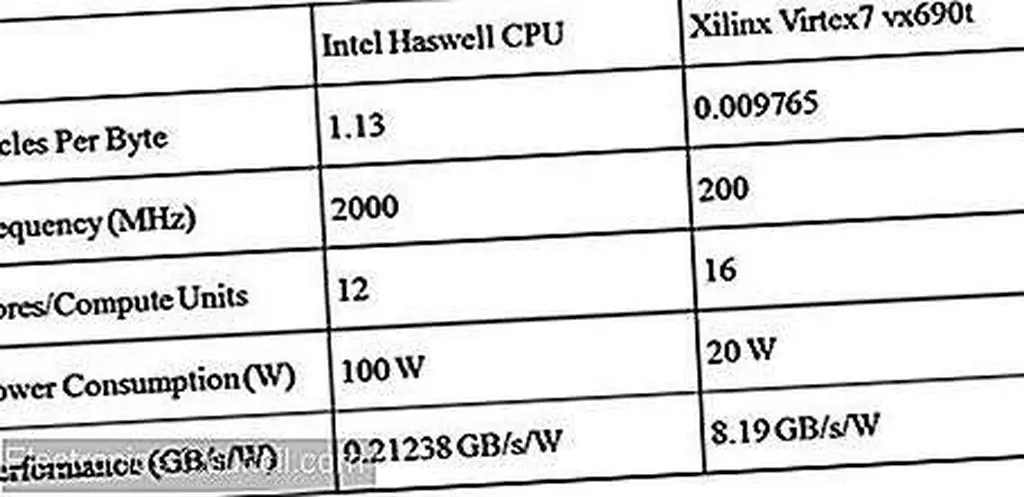

Реализация FPGA функции SHA-1 показана на рисунке 4. В этой конструкции ключевым элементом является создание пользовательского вычислительного блока для охвата 80 раундов обработки, необходимых для вычисления одного SHA-1. Сгруппировав все 80 раундов обработки внутри одной и той же логики обработки, разработчик приложения минимизирует взаимодействия с элементами кэша или памяти, как это требуется в стандартной реализации ЦП. Это, в свою очередь, увеличивает пропускную способность для этой функции и снижает потребляемую мощность, необходимую для поддержания достигнутой пропускной способности. Преимущества реализации FPGA и реализации ЦП обобщены в следующей таблице:

Для этого сравнения процессор Intel Haswell имеет 12 ядер, способных выполнять любой код ядра OpenCL, но не оптимизированный для какой-либо конкретной рабочей нагрузки. Напротив, реализация FPGA имеет 16 ядер, оптимизированных для выполнения только рабочей нагрузки SHA1. Разница в уровне настройки для блока вычисления ускорителя напрямую переводится в разницу производительности между двумя устройствами для этой рабочей нагрузки.

Результаты FPGA Xilinx были сгенерированы путем компиляции алгоритма SHA1 с использованием среды разработки SDAccel для OpenCL, C и C + и запуска результирующего двоичного файла программы на устройстве Xilinx Virtex 7. SDAccel обеспечивает до 25 раз лучшую производительность / ватт для ускорения приложений для центров обработки данных с использованием FPGA и объединяет первый в отрасли архитектурно оптимизирующий компилятор, поддерживающий любую комбинацию ядер OpenCL, C и C +, а также библиотеки, платы разработки и первый полный процессор / графический процессор -подобного развития и времени работы для ПЛИС.

ПО BY: SPENSER GILLILAND, FERNANDO MARTINEZ VALLINA и VINAY SINGH, Xilinx, www.xilinx.com