Комбинированная схема проектирования и моделирования с использованием ворот

Конструкция контура с ограниченными входами входов

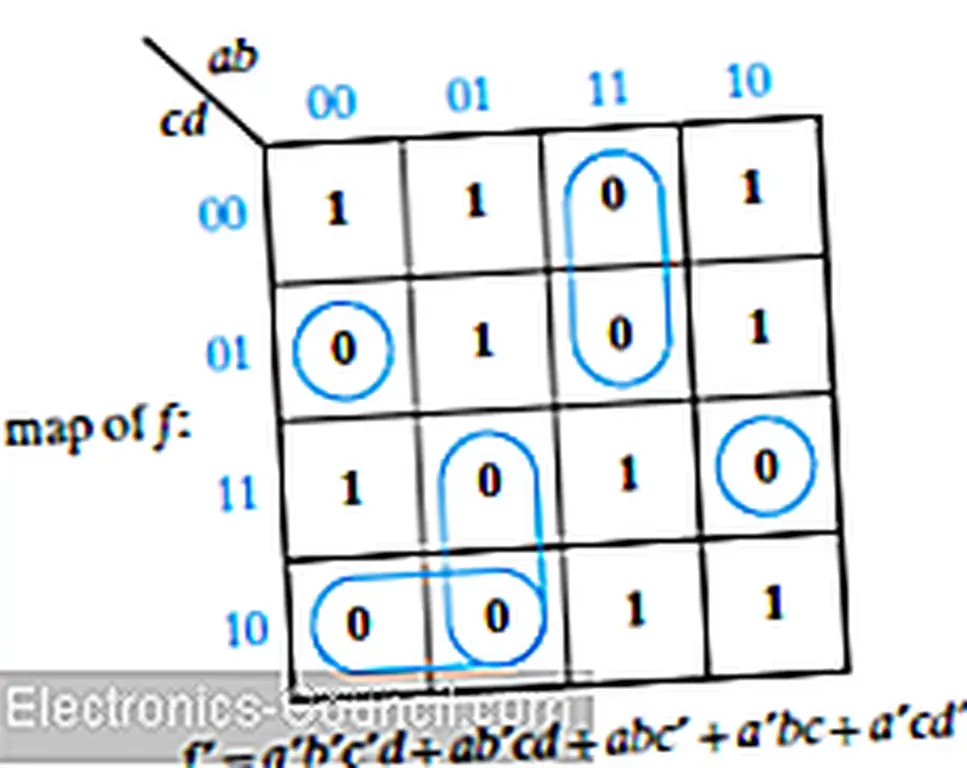

В любой практической конструкции логических схем максимальные входы, которые может иметь вентиль (вентилятор), ограничены. Это число может варьироваться от двух, трех, четырех, восьми или некоторых других чисел, в зависимости от типа ворот, используемых при проектировании схемы. Если какая-либо двухуровневая реализация схемы требует большего количества входных сигналов, чем разрешено, логическое выражение может быть учтено для получения многоуровневой реализации. Ниже приведен пример, который просит реализовать $$ f (a, b, c, d) = \ sum m (0, 3, 4, 5, 8, 9, 10, 14, 15) $$ с помощью трех входных Ворота НОР.

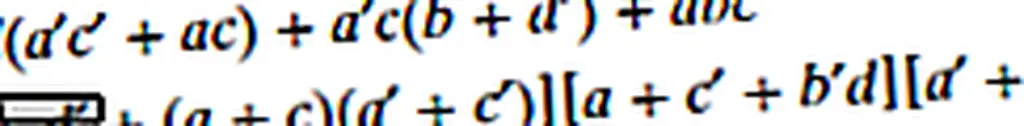

Это выражение представляет собой двухуровневую реализацию; однако для этого требуется два входа с четырьмя входами и один вход с пятью входами. Это требование не является идеальным способом разработки любой функциональной комбинационной схемы. Чтобы уменьшить это выражение, f 'учитывается для уменьшения максимального количества входов затвора. После факторизации этого логического выражения количество входов затвора может быть уменьшено до трех, как показано ниже.

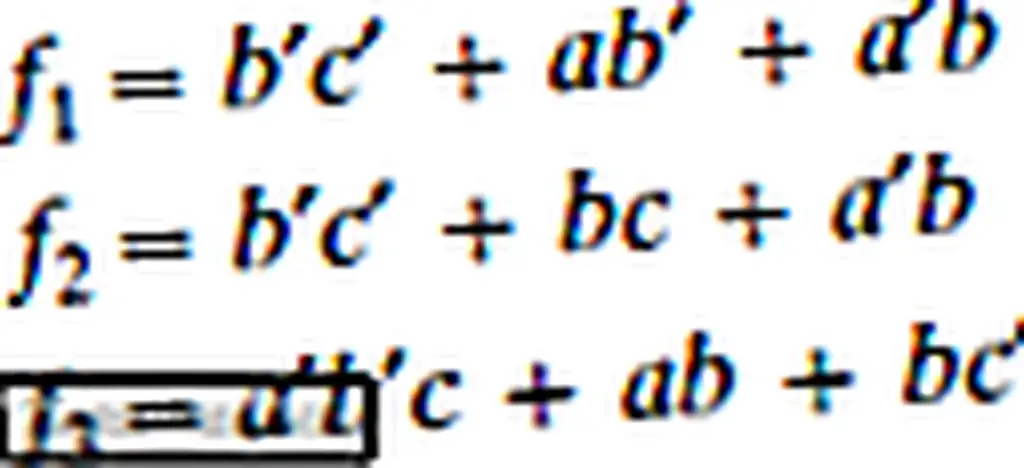

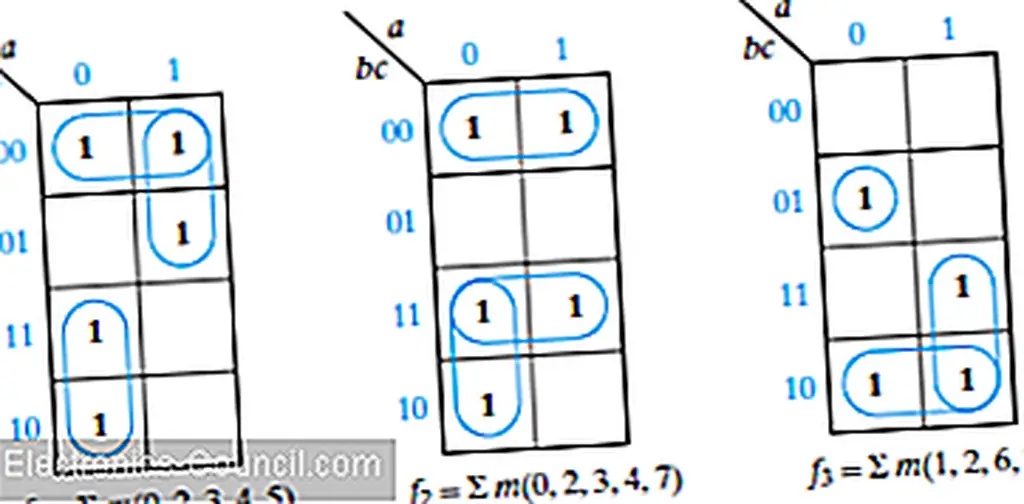

При проектировании большой выходной цепи с более чем двумя уровнями наилучшей техникой было бы минимизировать каждую функцию отдельно. Чтобы увеличить количество уровней, должны быть учтены двухуровневые логические выражения. Когда факторинг, введение общих терминов, где это возможно, является самым идеальным способом упрощения. Ниже приведен еще один пример, который просит реализовать логические функции, используя ТОЛЬКО два входа NAND и инверторы. Минимизировав каждую логическую функцию по отдельности, можно было бы найти:

Этот результат показывает, что для каждой логической функции требуется один входной логический элемент с тремя входами. Чтобы использовать логический элемент ИЛИ для каждой функции, сокращение ввода затвора путем факторинга выполняется ниже.

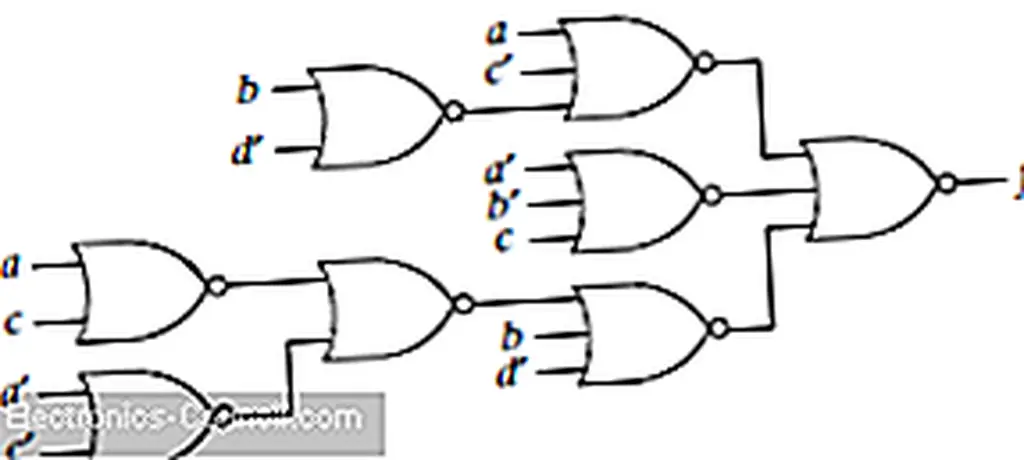

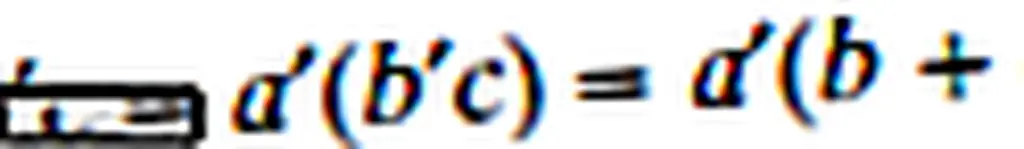

При внимательном рассмотрении логическое выражение f 2 имеет общий термин с f 1 of ab, поэтому, используя второе выражение f 2, последний три входной затвор из f 3 можно устранить, как показано ниже:

Результирующая логическая схема, использующая общие термины a'b и a + c ', имеет OR на каждом выходе. Преобразование в ворота NAND является простым, как показано на правой стороне рисунка.

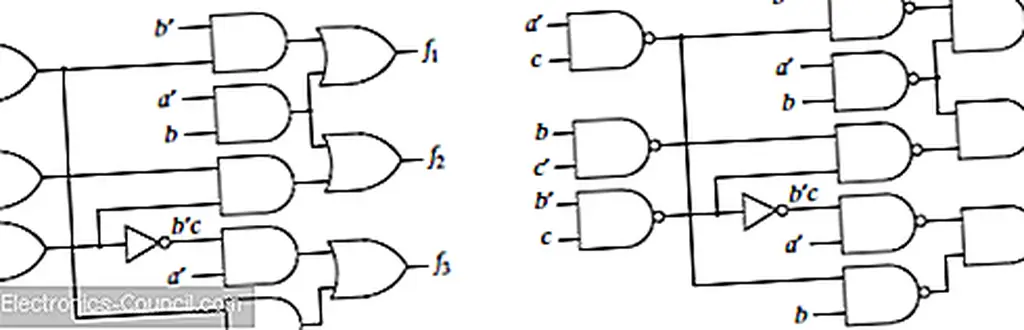

Задержки в воротах и диаграммы времени

Если вход логического затвора изменен, выход не изменится мгновенно. Причина этого заключается в том, что элементы, которые переключают входы в пределах затвора, фиксируют время, чтобы реагировать на изменение, поэтому результирующий результат изменения задерживается относительно входа. Задержка распространения в показателе инвертора, показанная ниже любых возможных сигналов ввода и вывода для инвертора. Для изменения выхода, задержанного по времени, $$ \ varepsilon $$, принятого с уважением на вход, говорят, что имеет задержку распространения $$ \ varepsilon $$. Задержка распространения для изменения вывода от 0 до 1 может отличаться от задержки задержки для изменения от 1 до 0. Некоторыми задержками распространения можно пренебречь, если они сокращаются до нескольких наносекунд. Однако рекомендуется анализировать эти последовательные схемы, какими бы короткими они ни были.

Скорее всего, для анализа последовательных схем будет использоваться временная диаграмма. Временные диаграммы могут использоваться для отображения разных сигналов в цепи в зависимости от времени. При построении множества переменных они строятся по одному и тому же масштабу времени, поэтому время, в которое эти переменные изменяются относительно друг друга, может быть легко понято.

Для схемы с двумя воротами, как показано ниже, предполагается, что каждый затвор имеет задержку распространения 20 нс. Диаграмма указывает, что произойдет, если входные входы B и C будут удерживаться при регулярных значениях 1 и 0 соответственно, а вход A затвора будет изменен на 1 при t = 40 нс, где затем будет изменен на 0 при t = 100 нс, Выход ворот G 1 изменяется ровно через 20 нс после изменения A, и, наконец, выход ворот G 2 изменяется ровно через 20 нс после изменения G 1.

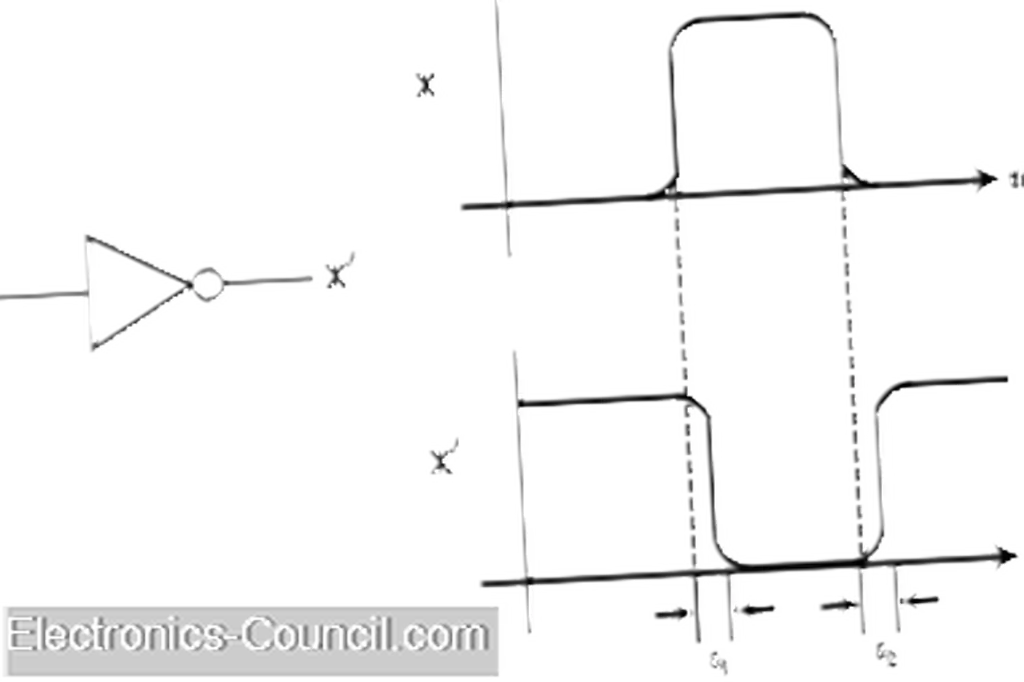

На рисунке ниже изображена временная диаграмма для логической схемы с элементом задержки. Вход X состоит из двух импульсов: первый импульс имеет ширину 2 микросекунды, а второй импульс - 3 микросекунды. Элемент задержки, касательный от X, имеет выход Y, который идентичен входу, X, но он задерживается на 1 микросекунду. Это означает, что Y изменяется от значения 1, 1 микросекунды после нарастающего фронта импульса X и затем возвращается к значению 0, 1 микросекунды после падения фронта импульса X. Z, который является выходом этого логического элемента И, всегда должен быть равным 1 в течение временного интервала, для которого как X, так и Y имеют значение 1. Предполагая, что существует небольшая задержка распространения в логике AND $$ \ varepsilon $$, то на выходе Z будет представлена следующая временная диаграмма:

Прибытие

На этом этапе у вас должно быть понимание того, как нарисовать временную диаграмму для любой комбинационной схемы с задержками затвора и без него, понимание проектирования и упрощения двух или нескольких логических схем уровня, а также полное понимание того, как влияют временные задержки операции затвора. Еще одна тема, которая будет изучена, - это опасности в схемах комбинационных логических схем, в частности, поиск статических 0- и 1-опасных факторов.