Как оптимизировать переходный отклик цикла с фазовой блокировкой

В этой статье мы рассмотрим математические отношения, которые помогут вам спроектировать PLL, который быстро и плавно блокирует входную частоту.

Вспомогательная информация

-

То, что точно является фазовой блокировкой, в любом случае "" src = "// www.allaboutcircuits.com/uploads/articles/techarticle_WIPLL_diagram.jpg" />

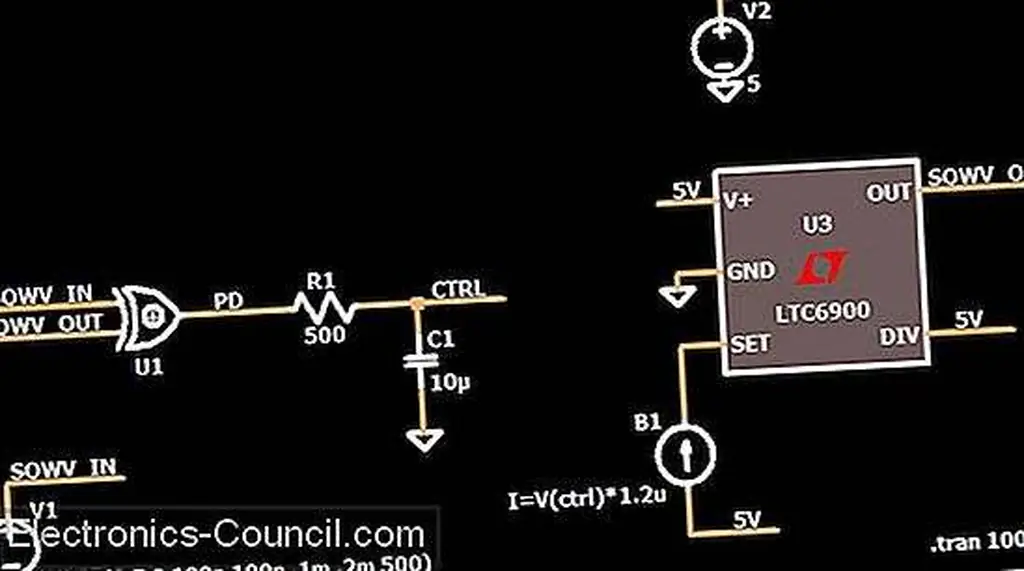

Image В этой статье описывается, как создать петлевой фильтр для оптимального переходного отклика, но, как вы увидите, этот процесс проектирования не может возникать «изолированно», поскольку на переходный отклик влияет также усиление фазового детектора и усиление ГУН.

Сглаживание / фильтрация / Усреднение

Если вы прочитали предыдущие статьи PLL, вы уже знаете, почему система должна включать фильтр нижних частот: нам нужно что-то, что преобразует выходной сигнал фазового детектора в медленно меняющееся напряжение, которое можно использовать для регулировки частоты напряжения управляемый осциллятор. Существуют различные способы концептуализации этого:

- Фильтр нижних частот ослабляет высокочастотные компоненты в выходном сигнале PD, так что низкочастотное поведение становится доминирующим.

- Выходной сигнал PD эквивалентен сигналу PWM, и фильтр сглаживает его на соответствующий уровень аналогового сигнала.

- Фильтр обеспечивает математическую функциональность извлечения среднего значения из вывода PD.

Это все допустимые интерпретации, и если для вас есть больше смысла, чем другие, обязательно сосредоточитесь на нем. Критическим шагом в понимании (и запоминании) является формирование образов и связей, которые гармонируют с вашими собственными когнитивными особенностями.

Математика

Строгий математический анализ переходного поведения ФАПЧ не является прямым. Однако мы можем получить адекватные результаты оптимизации, используя довольно простое линейное приближение. В этом приближении передаточная функция назначается каждому из трех функциональных блоков. Если вы объедините их в одну функцию передачи, которая описывает всю PLL, вы получите выражение второго порядка, которое можно использовать для нахождения уравнений для собственной частоты PLL и коэффициента демпфирования. Это система второго порядка (т. Е. Двухполюсная), потому что фильтр нижних частот вносит один полюс, а VCO - один полюс; таким образом, это приближение справедливо только с ФНЧ первого порядка.

Я не думаю, что вам нужно слишком беспокоиться о математических деталях; главное, что мы можем использовать коэффициент демпфирования, чтобы помочь нам разработать фильтр нижних частот. Вот уравнение для коэффициента демпфирования PLL (обычно обозначаемого ζ, но я буду использовать DR):

$$ DR = \ гидроразрыва {1} {2} SQRT { гидроразрыва { omega_ {ФНЧ}} {K}} $$

Как вы можете видеть, между коэффициентом демпфирования и частотой отсечки LPF существует довольно простая связь. Возникают два вопроса:

- Что такое K?

- Какую ценность мы должны использовать для DR?

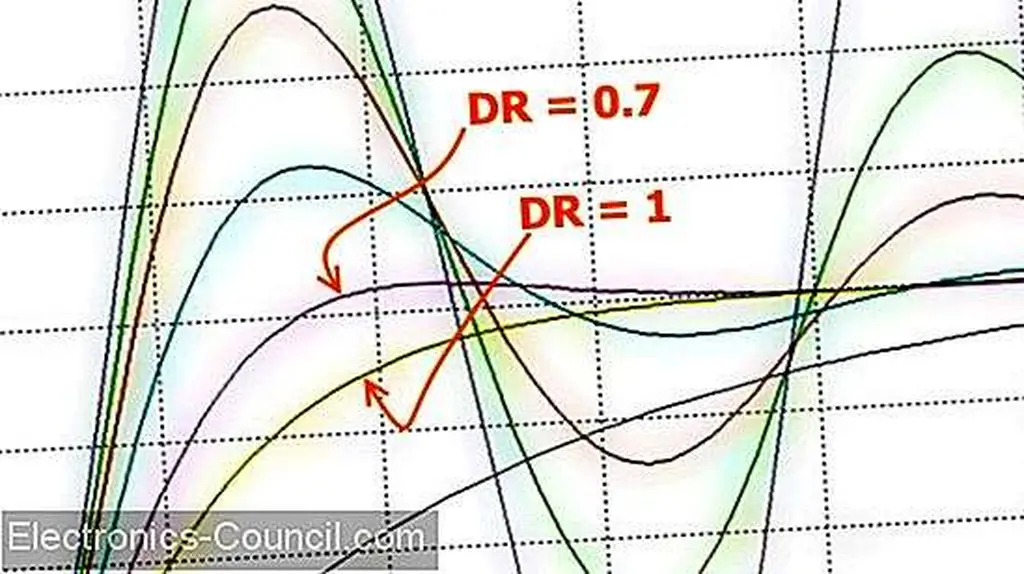

Второй вопрос проще первого. Мы моделируем PLL как типичную систему управления второго порядка, а это означает, что применяются те же самые принципы демпфирования: если DR слишком низок, реакция шага проявит чрезмерное колебание. Если он слишком высок, система займет много времени, чтобы достичь стационарного состояния. Как показано на следующем графике, идеальный DR составляет около 0, 7 (если вы хотите, чтобы система немного поддалась), около 1, 0 (если вы хотите, чтобы система немного завышена) или где-то посередине.

Image Теперь все, что нам нужно, это K, который представляет общий выигрыш системы; он рассчитывается путем умножения коэффициента усиления фазового детектора на коэффициент усиления ГУН. К сожалению, здесь все усложняется.

Закон о частоте / коэффициенте усиления / обрезания частоты

Предположим, что у вас есть коэффициент фазового детектора 1 В / радиан (это означает, что один радиан разности фаз между двумя входами приведет к 1 В амплитуды выходного сигнала). Предположим также, что увеличение управляющего напряжения на 1 В увеличивает частоту ГУН на 1000 Гц; так как 1000 Гц ≈ 6283 рад / с, наш коэффициент усиления VCO составляет 6283 (рад / с) / В.

$$ K = K_ {PD} times K_ {VCO} = 1 \ frac {V} {rad} times6283 \ frac {rad / s} {V} = 6283 \ s ^ {- 1} $$

Если мы хотим, чтобы DR = 1, мы будем иметь следующее уравнение:

$$ 1 = \ frac {1} {2} sqrt { frac { omega_ {LPF}} {6283 \ s ^ {- 1}}} $$

После немного математики мы заканчиваем ω LPF = 25132 рад / с. Преобразуя назад в герц, мы видим, что частота среза фильтра нижних частот должна составлять 4 кГц. Это кажется вполне разумным результатом, но если вы обдумаете это число на минуту, вы можете начать распознавать проблему: что произойдет, если мы хотим использовать PLL с частотами, которые ниже или сопоставимы с частотой отсечки LPF? Цель фильтра нижних частот состоит в том, чтобы сгладить форму сигнала фазового детектора, но это произойдет только тогда, когда частота отсечки фильтра будет значительно ниже частот, генерируемых PD.

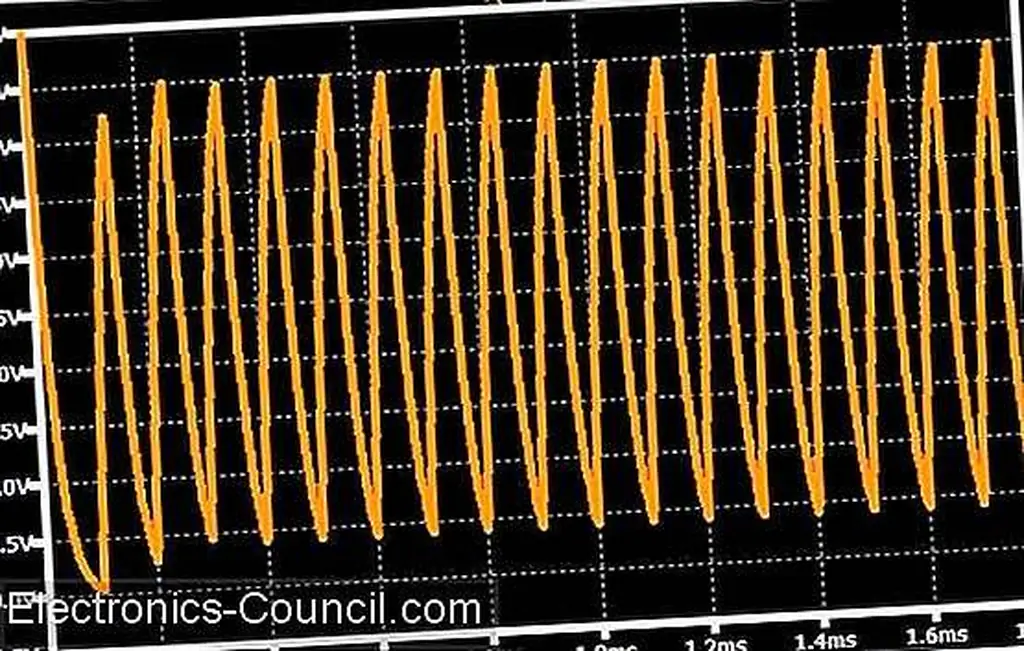

В качестве примера, если я вычислил общий коэффициент усиления PLL LTspice и затем сконструировал RC-фильтр на основе этого усиления и DR = 1, мое управляющее напряжение выглядит следующим образом:

Image Основная проблема здесь заключается в том, что ω LPF не может (как я сказал, к началу статьи) выбирать отдельно. Как вы можете видеть в приведенном выше уравнении DR, определенный DR требует определенного отношения между ω LPF и K, а ω LPF в свою очередь ограничивается предполагаемым диапазоном частот PLL. Таким образом, оптимизация переходных процессов - это не просто поиск K, а затем вычисление частоты отсечки LPF. Скорее, вы должны убедиться, что значение K достаточно мало, чтобы вы могли выбрать частоту среза, которая является достаточно низкой для ожидаемой операционной среды PLL, а затем вы можете точно настроить частоту среза, используя уравнение, которое связывает DR с ω LPF и K.

Вывод

В этой статье был представлен немного математического анализа PLL, чтобы объяснить процедуру проектирования PLL, которая обеспечивает блокировку частоты без чрезмерных колебаний или чрезмерной задержки. Простое уравнение позволяет рассчитать соответствующую частоту отсечки LPF, основанную на общем усилении PLL и требуемом коэффициенте демпфирования, но коэффициент усиления должен быть достаточно низким, чтобы обеспечить частоту среза, которая обеспечивает достаточное ослабление высокочастотных компонентов в PD выходной сигнал.

Мы продолжим изучение этой темы в следующей статье.