Как использовать переносные помощники для эффективного внедрения многооперационных дополнений

В этой статье рассматривается использование переносчиков сбережений, чтобы эффективно вычислять многооперационное дополнение.

Есть много обстоятельств, в которых нам нужно добавить набор чисел вместе. Например, рассмотрим вычисление скалярного произведения двух векторов длины n, $$ A = (a_1, a_2, \ dots, a_n) $$ и $$ B = (b_1, b_2, \ dots, b_n) $$. В этом случае нам нужно вычислить

$$ AB = a_1b_1 + a_2b_2 + \ dots + a_nb_n $$

Как вы можете видеть, скалярное произведение двух векторов длины n требует добавления набора из n чисел вместе.

Многооперационное добавление с использованием двухоператорного сумматора

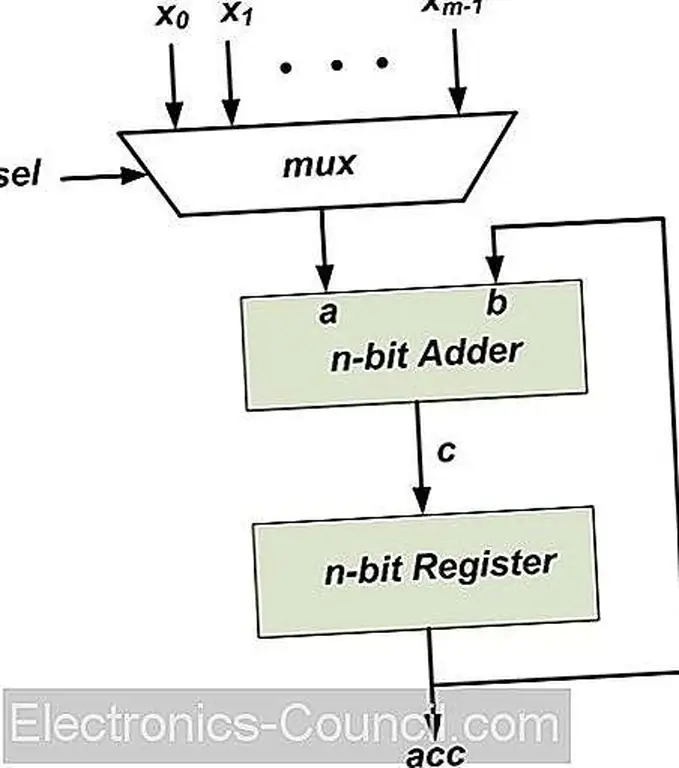

Мы можем использовать один двухоператорный сумматор последовательно для выполнения многооперационного добавления. Предположим, что нам нужно добавить m чисел вместе, то есть $$ x_0 + x_1 + \ dots + x_ {m-1} $$. Кроме того, предположим, что сумма этих чисел, acc, может быть представлена n битами. Для этого добавления мы можем использовать блок-схему на рисунке 1.

Рисунок 1

В начале вычислений регистр n- бит сбрасывается до нуля. Затем первый операнд, $$ x_0 $$, выбирается мультиплексором и применяется к n- разрядному сумматору. Другой вход сумматора, b, поступает из регистра n- бит. Следовательно, на этом этапе выход n- разрядного сумматора будет $$ c = x_0 + 0 = x_0 $$. С предстоящим тиком часов это будет храниться в регистре n -bit, то есть $$ acc = x_0 $$.

Затем второй мультиплексор выбирает второй операнд $$ x_1 $$. Это будет добавлено к текущему значению регистра n- бит, который дает $$ c = x_1 + acc = x_1 + x_0 $$. При следующем фронте тактового сигнала значение регистра n- бит будет $$ acc = x_1 + x_0 $$. Эта процедура будет повторяться для остальных операндов. С каждым тиком часов будет добавлен новый операнд, и результат будет сохранен в регистре n- бит. Обратите внимание, что нам понадобится блок управления для генерации соответствующего сигнала для ввода ввода мультиплексора.

Задержка многооперационного добавления с использованием двухоператорного сумматора

В структуре на рисунке 1 используется один сумматор для выполнения многооперационного добавления, в результате он эффективен с точки зрения аппаратного обеспечения, но он не эффективен с точки зрения запаздывания. Давайте рассмотрим задержку этой структуры. Основной временной задачей описанной выше процедуры является добавление двух n- разрядных чисел. Если мы рассмотрим задержку $$ T_ {n-bit-adder} $$ для n-разрядного сумматора, то задержка добавления m чисел может быть приблизительно оценена как $$ m \ times T_ {n-бит-сумматор } $$

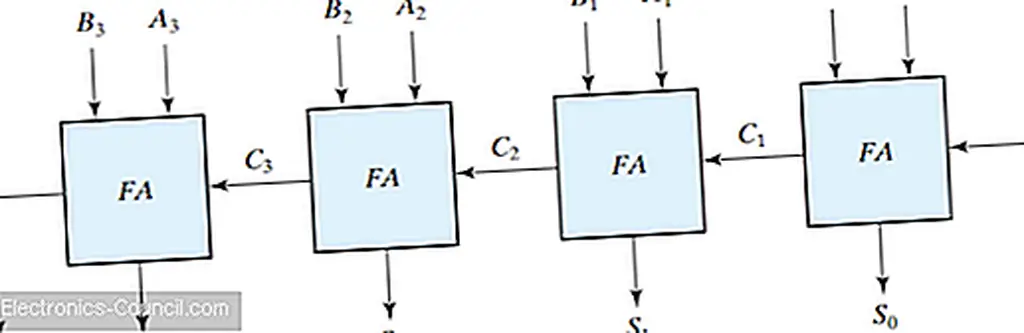

Существует множество разнообразных конфигураций для реализации n- разрядного сумматора, но для того, чтобы все было просто, мы предполагаем, что используется простой суммирующий суммирующий рябь. Структура четырехбитового сумматора, несущего пульсацию, показана на рисунке 2.

Рисунок 2. Структурная схема четырехбитового ряби. Изображение предоставлено Digital Design

На этом рисунке для вычисления $$ S_3 $$ и $$ C_4 $$ требуется перенос $$ C_3 $$. Следовательно, задержка этой схемы будет в четыре раза больше задержки полного сумматора (FA) $$ T_ {FA} $$. Точно так же задержка n- битного суммирующего суммирования будет $$ n \ times T_ {FA} $$. Поэтому задержка схемы на рисунке 1 может быть приблизительно оценена как $$ m \ times T_ {n-bit-adder} = m \ times n \ times T_ {FA} $$. По мере увеличения количества операндов, m и числа бит n увеличивается, задержка схемы увеличивается.

Мы можем ускорить вычисления, используя другие структуры для n- разрядного сумматора. Например, мы можем использовать структуру отслеживания переноса, но эти методы обычно значительно повышают сложность системы.

Существует интересный метод, а именно: суммирующий носитель, который может использоваться для эффективного использования многооперационного сумматора без значительного увеличения используемого оборудования. В следующем разделе статьи мы рассмотрим причины медленной работы вышеуказанной структуры, затем рассмотрим метод переноса.

Причины для замедления

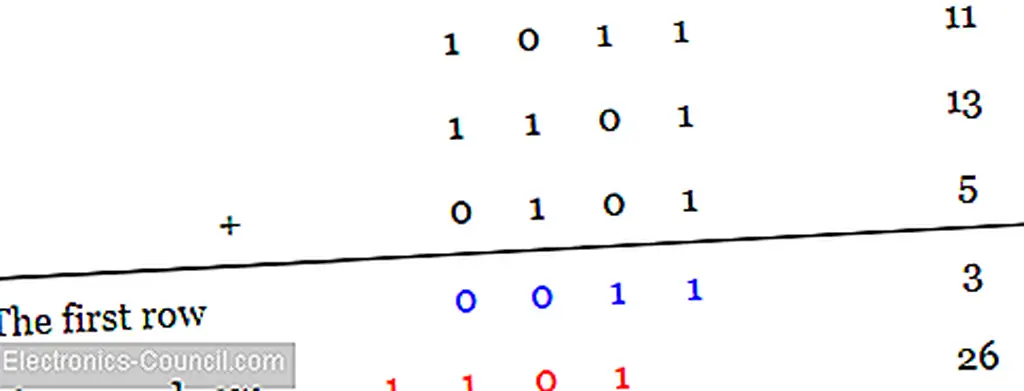

Как мы можем ускорить добавление вышеперечисленного множителя? "Src =" // www.allaboutcircuits.com/uploads/articles/Fig_of_Cal1.png" />

Добавляя три бита из первого столбца, мы имеем $$ 1 + 1 + 1 = 11_2 = 3_ {10} $$. Обычный способ добавления добавляет полученный перенос к цифрам следующего положения бит. Здесь мы просто записали результат первого столбца в первой строке наших вычислений. Транспортировка, полученная на этом этапе расчетов, показана красным цветом во втором положении бит.

Аналогично, для второй разрядной позиции операндов мы имеем $$ 1 + 0 + 0 = 01 $$. Эти два бита написаны во второй строке наших вычислений. Обратите внимание, что эти два бита, $$ 01 $$, должны быть записаны под вторым и третьим столбцами. Следовательно, десятичный эквивалент этого этапа сложения будет два, а не один. Транспортировка с этого этапа показана красным цветом в позиции третьего бита. Мы повторим эту процедуру для следующих двух столбцов. Учитывая эквивалентные десятичные значения, мы можем проверить, что добавление полученных чисел дает правильную сумму, то есть $$ 11 + 13 + 5 = 3 + 2 + 8 + 16 $$. На самом деле мы получили новое представление для данного трех операнда.

Теперь обратите внимание, что в каждом столбце нашего нового представления есть только два бита (другими словами, в каждом столбце может быть не более двух ненулевых битов). Следовательно, мы можем изменить это дополнение и заменить его на двух операндов, как показано ниже:

Здесь перенос, создаваемый каждым столбцом, записывается в следующем столбце во второй строке наших вычислений (бит в красном). Остальные биты записываются в первой строке синим цветом. Как видите, новое представление дает правильную сумму, то есть $$ 11 + 13 + 5 = 3 + 26 $$.

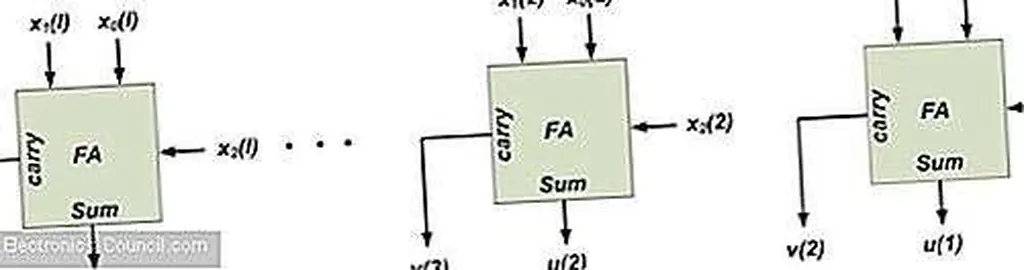

Этот пример показывает, что мы можем эффективно уменьшить добавление из трех операндов в дополнение к двум операндам. Следует отметить, что мы работали над битами каждого столбца независимо друг от друга. Другими словами, мы можем использовать специализированное оборудование для вычисления двухбитового эквивалента разных столбцов одновременно. Это контрастирует с работой сумматора, несущего пульсацию, который не может вычислить сумму перед вычислением сигналов переноса предыдущих позиций бит. Также обратите внимание, что полный сумматор - это, по сути, аппаратное обеспечение, которое вычисляет двухбитное представление для трех бит столбцов. Работая с номерами l -bit, нам понадобится l полных сумматоров для преобразования трех операндов ($$ x_0 + x_1 + x_2 $$) в дополнение к двум операндам ($$ u + v $$). Блок-схема такого преобразователя показана на рисунке 3.

Рисунок 3. 1-битный суммирующий носитель

Эта схема имеет сходство с суммируемым рябителем на фиг. 2; однако здесь перенос не распространяется на следующую позицию бит, а хранится для будущих вычислений. Вот почему структура на рисунке 3 называется суммирующим носителем. Все FA-устройства с суммируемым носителем работают параллельно. Также обратите внимание, что индекс для v- сигнала, который сохраняет перенос, создаваемый разными позициями битов, начинается с двух, v (2), а не с v (1). Это можно понять из приведенного выше численного примера.

Для приведенного выше численного примера есть четыре столбца, и нам понадобится четыре FA, чтобы преобразовать добавление трех операндов в дополнение к двум операндам. Поскольку все эти FA работают параллельно, задержка этого преобразования будет равна задержке одного FA, $$ T_ {FA} $$. Теперь мы можем использовать четырехбитовый сумматор для выполнения окончательного добавления двух операндов. Следовательно, общая задержка будет $$ T_ {FA} + T_ {четырехбитовый-сумматор} = T_ {FA} +4 \ times T_ {FA} = 5 \ times T_ {FA} $$. С блок-схемой, изображенной на рисунке 1, нам нужно будет использовать пятибитовый сумматор, а задержка будет равна $$ m \ times n \ times T_ {FA} = 3 \ times 5 \ times T_ {FA} = 15 \ times T_ {FA} $$.

Преобразование многооператорного дополнения в дополнение к двум операндам

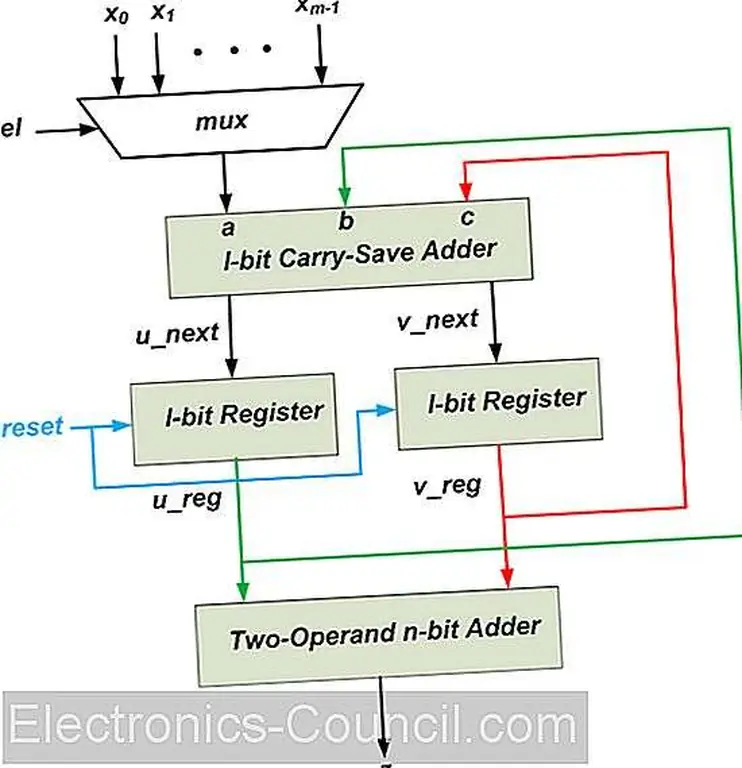

В предыдущем разделе мы увидели, что сумматор с переносом может заменить добавление трех операндов, $$ x_0 + x_1 + x_2 $$, с добавлением двух операндов, $$ u + v $$, где $$ x_0 + x_1 + x_2 = и + v $$. Повторно применяя концепцию суммирующего переноса, мы можем преобразовать многооперационное дополнение в дополнение к двум операндам. Предположим, что нам нужно добавить m l -битных чисел вместе, то есть $$ x_0 + x_1 + \ dots + x_ {m-1} $$. Кроме того, предположим, что сумма этих чисел z может быть представлена n битами. Для этого добавления мы можем использовать блок-схему на рисунке 4.

Рисунок 4

Существует два l- битных регистра, в которых хранятся значения сигналов u_next и v_next, рассчитанные с помощью l -bit carry-save-сумматора. Операнды применяются к суммируемому носителю по одному через мультиплексор. Остальные входы переносного сейдера поступают из регистров l -bit u и v. В начале вычислений регистры l -bit сбрасываются до нуля. В результате приведенная выше схема фактически вычисляет сумму $$ 0 + 0 + x_0 + x_1 + \ dots + x_ {m-1} $$, которая, очевидно, равна требуемой сумме $$ x_0 + x_1 + \ dots + x_ {m- 1} $$. Во-первых, $$ x_0 $$ выбирается мультиплексором, а добавление трех операндов $$ 0 + 0 + x_0 $$ применяется к суммируемому сальдо. Сигналы u_next и v_next, полученные на этом этапе, будут сохранены в соответствующих регистрах на предстоящем такте.

Затем следующий операнд, $$ x_1 $$, выбирается мультиплексором и применяется к сумматору с 1- битным переносом. Остальные входы суммирующего сальдо, b и c, поступают из l- битных регистров, которые представляют сумму $$ 0 + 0 + x_0 $$. Следовательно, на этом этапе сумма $$ 0 + 0 + x_0 + x_1 $$ будет представлена двумя сигналами u_next и v_next. Эти значения будут сохранены в соответствующих регистрах на предстоящем такте. Эта процедура будет повторяться для остальных операндов. Наконец, m -operand добавление $$ x_0 + x_1 + \ dots + x_ {m-1} $$ будет представлено с использованием только двух сигналов u_reg и v_reg. Теперь мы можем использовать двухоперационный n- разрядный сумматор для вычисления u_reg + v_reg, который равен $$ x_0 + x_1 + \ dots + x_ {m-1} $$. Обратите внимание, что нам понадобится блок управления для генерации соответствующего сигнала для ввода ввода мультиплексора. Оценка задержки вышеуказанной схемы остается в качестве упражнения для читателя.

Для получения дополнительной информации прочтите главу 8 «Компьютерная арифметика: алгоритмы и аппаратные средства» и глава 7 «Руководство по реализации Арифметических функций ПЛИС».

Резюме

- Есть много обстоятельств, в которых нам нужно добавить набор чисел вместе.

- Мы можем использовать один двухоператорный сумматор последовательно для выполнения многооперационного добавления. Такое многооперационное дополнение является аппаратно эффективным, но оно неэффективно с точки зрения запаздывания.

- Работая с номерами l -bit, нам понадобится l полных сумматоров для преобразования трех операндов ($$ x_0 + x_1 + x_2 $$) в дополнение к двум операндам ($$ u + v $$).

- Повторно применяя концепцию суммирующего переноса, мы можем преобразовать многооперационное дополнение в дополнение к двум операндам.

Чтобы просмотреть полный список моих статей, перейдите на эту страницу.