Как имитировать цикл с фазовой блокировкой

В этой статье представлена схема LTspice, которая может использоваться для изучения поведения цикла с фазовой синхронизацией.

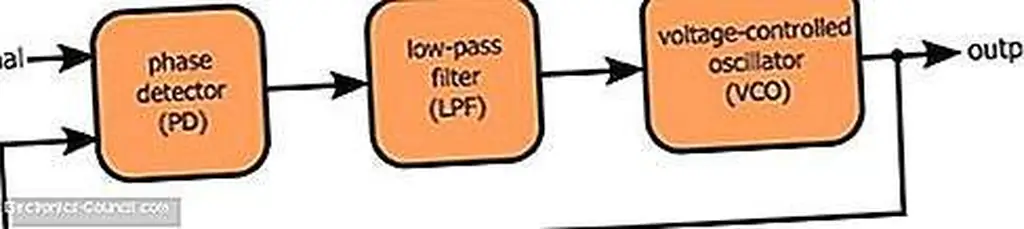

В предыдущей статье я представил основные понятия и основные функции системы с отрицательной обратной связью, известной как петля с фазовой синхронизацией (PLL). Как вы помните, самая основная PLL состоит из фазового детектора (фактически детектора разности фаз), фильтра нижних частот и управляемого напряжением генератора:

Первым выходным сигналом является периодический сигнал, создаваемый ГУН. При правильных обстоятельствах PLL гарантирует, что частота выходного сигнала точно равна частоте входного сигнала.

Я предпочитаю самостоятельно выполнять моделирование, а не полностью полагаться на графики и уравнения, созданные кем-то другим. Это касается практически любой схемы, но это особенно важно для PLL, потому что аналитическое исследование функциональности PLL, на мой взгляд, сбивает с толку и неадекватно.

Это особенно верно в отношении начального переходного ответа, то есть поведения, проявляемого PLL, когда он пытается заблокировать входной сигнал. Переходный ответ PLL не только неуловим, когда мы пытаемся достичь интуитивного понимания - он также нелинейный и нелегко переводится в уравнения. Фактически, реферат этого академического документа указывает, что даже «точное численное моделирование» может быть проблематичным, поскольку для этого требуется так много времени обработки.

Цепь

Существует множество способов моделирования PLL. Нет ничего особенного в схеме, которую я создал, но я думаю, что это хорошее место для начала по двум причинам: это концептуально просто и не перегружает движок SPICE (другими словами, нет необходимости брать кофе перерыв, пока вы ждете окончания моделирования).

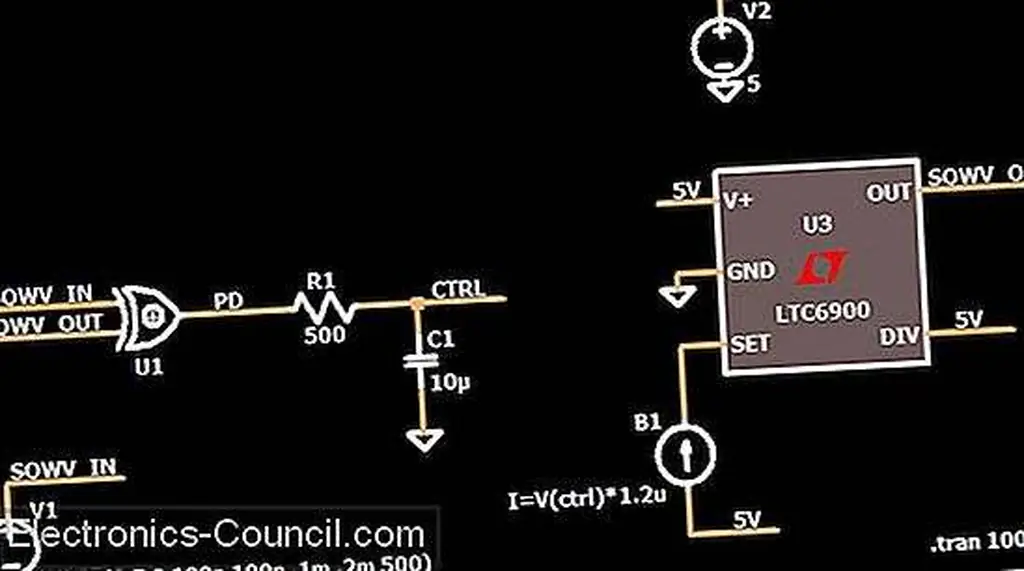

Это мой PLL PLspice:

Два из трех функциональных блоков очень просты. Фазовый детектор является XOR-затвором (я использую описанную здесь библиотеку), а фильтр нижних частот представляет собой однополюсную RC-цепь. Из того, что я понимаю, даже PLL профессионального качества могут часто достигать адекватной производительности с помощью не более чем RC-прохода. Я попробовал фильтр второго порядка в своей симуляции, и схема RC работала лучше. Мне кажется, что дополнительное подавление пульсаций, обеспечиваемое фильтром второго порядка, просто необязательно.

VCO

Менее простой частью системы является блок VCO. Вместо специально разработанной схемы, такой как осциллятор Colpitts с переменной частотой, я решил сэкономить некоторое время и энергию, используя макромодель для ИС линейного синтезатора Linear Tech.

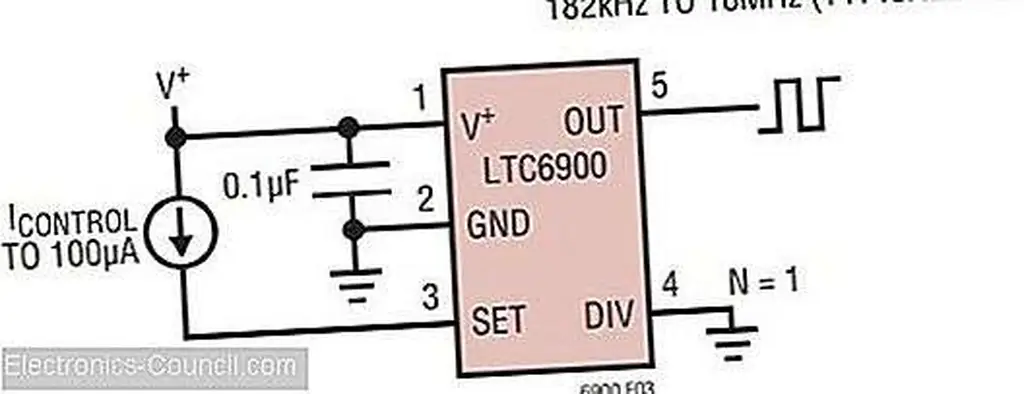

LTC6900 поддерживает частоты от 1 кГц до 20 МГц. Несмотря на то, что он называется осциллятором «резистор-набор», вы также можете управлять частотой, напрямую регулируя количество тока, поступающего в контакт SET. Это неудивительно, поскольку резистор (подключенный между SET и V +) является просто средством установления тока, текущего в вывод SET, который удерживается внутренней схемой при напряжении V + минус ~ 1, 1 В.

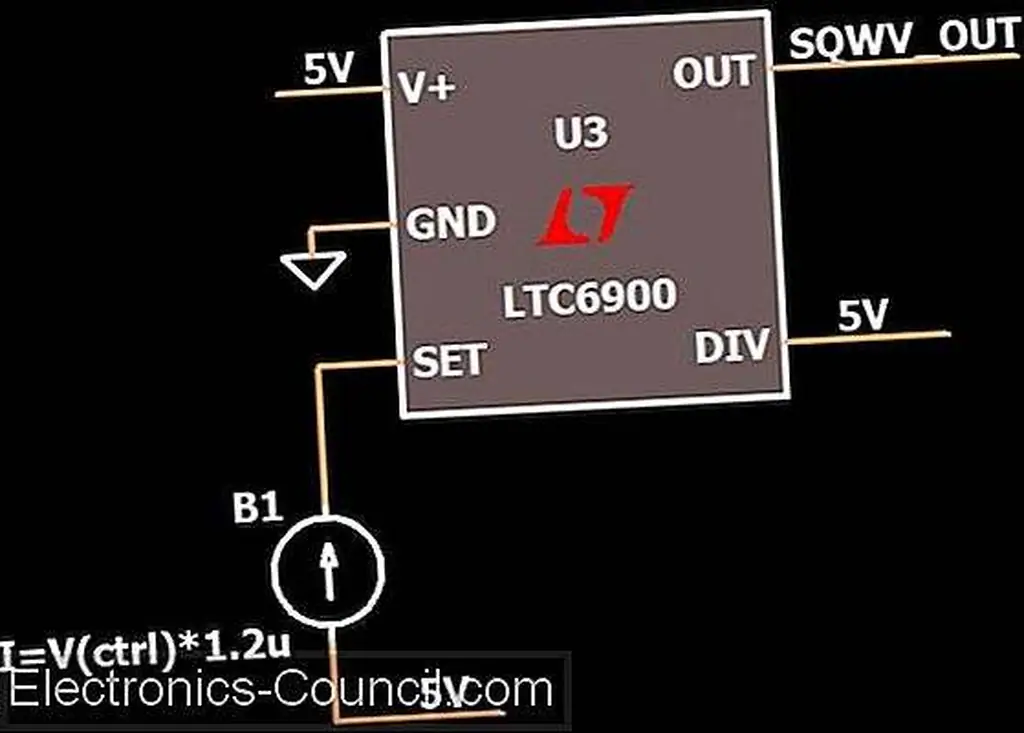

Как вы можете видеть, моя реализация LTC6900 аналогична:

Первое различие заключается в том, что вывод DIV составляет 5 V вместо земли (потому что мне нужны более низкие частоты). Другое изменение, которое я сделал (не удивительно, учитывая цель здесь), заключается в том, что вместо постоянного источника тока у меня есть источник тока с контролируемым напряжением. Это самая тонкая часть схемы, поэтому давайте поближе рассмотрим.

От напряжения к току до частоты

Сигнал фазового детектора с низким пропусканием фильтров служит в качестве управляющего напряжения для VCO. Я упростил свою схему, используя математические отношения вместо компонентов, чтобы перевести с управляющего напряжения на управляющий ток. Ток, текущий в вывод SET, определяется (с использованием произвольного поведенческого источника тока) в качестве напряжения в узле CTRL, умноженном на константу.

Следующий шаг - определить константу. Мы знаем, что наша входная частота составляет 5 кГц, и, следовательно, VCO в конечном итоге должна опираться на выходную частоту 5 кГц. В результате проб и ошибок я определил, что VCO будет генерировать сигнал 5 кГц, когда ток, текущий в вывод SET, составляет около 2, 9 мкА. Это первое, что нам нужно знать.

Затем нам нужно рассмотреть управляющее напряжение. Выход из фазового детектора переключается между землей и 5 В, что означает, что диапазон управляющего напряжения также составляет от 0 до 5 В. Нам нужно убедиться, что управляющее напряжение, соответствующее току SET-pin ~ 2, 9 мкА, будет где-то в пределах 0-5 В. И на самом деле, я хочу, чтобы конечное управляющее напряжение находилось где-то около середины диапазона, т. е. 2, 5 В. Таким образом, я просто делю 2, 9 мкА на 2, 5 В, чтобы определить фактор, который будет относиться ток SET-pin к управляющему напряжению.

$$ \ frac {2.9 \ mu A} {2.5 \ V} = 1.16 \ frac { mu A} {V} approx \ 1.2 \ frac { mu A} {V} \ \ Rightarrow \ \ I = (V_ {CTRL}) (1, 2 \ times10 ^ {- 6}) $$

Еще одна вещь, которую следует иметь в виду, состоит в том, что VCO должен быть совместим с током, который будет генерироваться, когда управляющее напряжение будет иметь максимальное значение. Мы не можем предсказать поведение запуска схемы, поэтому мы можем также предположить, что различия между фазой входных и выходных сигналов (или некоторых других начальных условий) могут приводить к высоким рабочим циклам фазового детектора и, как следствие, к высокому контролю напряжения. Если эти высокие управляющие напряжения приводят к неисправности VCO, у нас будут проблемы. В моей схеме LTspice V CTRL 5 В приводит к току SET-pin 6 мкА, который находится в допустимом диапазоне.

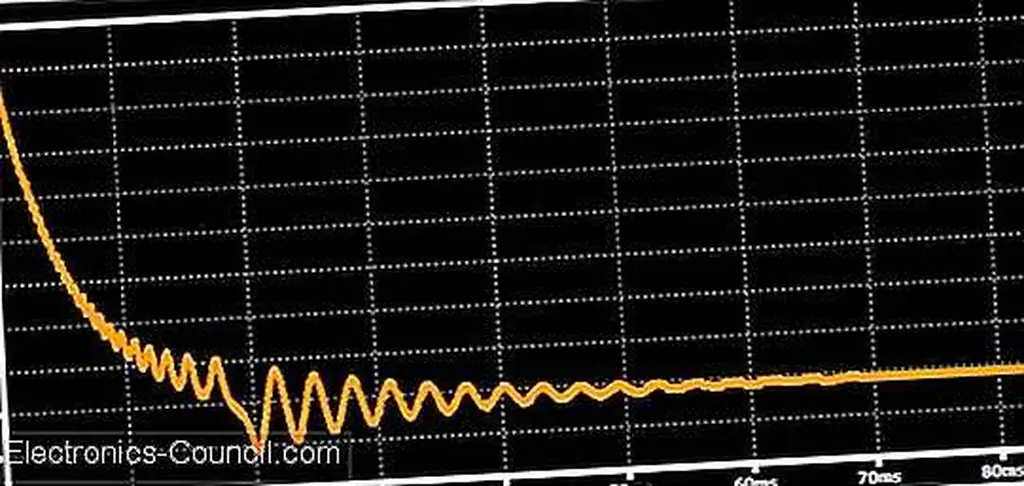

Мы рассмотрим детали и результаты моделирования в следующей статье. На данный момент я оставлю вас со следующим графиком, который показывает изменения в управляющем напряжении, когда PLL постепенно блокируется на входной частоте.

Вывод

В этой статье я представил и объяснил схему LTspice, которую я разработал для выполнения простых схемных схем с фазовой автоподстройкой. Переходный отклик проявляется на графике управляющего напряжения (т. Е. Выходе фильтра с фазовой характеристикой с низким пропусканием). Мы продолжим эксперимент PLL на основе SPICE в следующей статье.

Не стесняйтесь загружать мою схему LTspice, нажимая на оранжевую кнопку.

Схема LTspice