Как буферизовать выход Op-Amp для более высокого тока, часть 4

Если вы выбрали буфер с MOSFET вместо BJT, вам необходимо рассмотреть соотношение между емкостью и нестабильностью затвора.

Вспомогательная информация

- Введение в операционные усилители

- Изолированные транзисторы с полевым эффектом (MOSFET)

- Отрицательная обратная связь, часть 5: коэффициент усиления и фазовая маржа

Предыдущие статьи в этой серии

- Как буферизовать выход Op-Amp для более высокого тока, часть 1

- Как буферизовать выход Op-Amp для более высокого тока, часть 2

- Как буферизовать выход Op-Amp для более высокого тока, часть 3

Вопрос стабильности

В предыдущей статье мы увидели, что в стандартных схемах токовой буферизации операционных усилителей можно использовать MOSFET вместо BJT. Одним из существенных преимуществ реализации MOSFET является незначительный стационарный ток, требуемый от выходного каскада ОУ - ток стока МОП-транзистора контролируется главным образом напряжением затвор-источник, а не ток, текущий в затвор, и, кроме того, только небольшие (в нашем контексте, незначительные) течения утечки могут течь в ворота, поскольку они изолированы от остальной части полевого транзистора. Таким образом, вы можете генерировать очень большие токи нагрузки даже с очень слабым операционным усилителем. Однако изолированные ворота MOSFET являются преимуществом и обязательством. Этот изолированный затвор означает емкость, и в итоге вы столкнетесь с серьезной проблемой, если у вас слишком много емкости, подключенной к выходу op-amp.

На самом деле, это немного сложнее. Как вы, возможно, знаете, операционные усилители имеют ограниченную способность безопасно управлять емкостными нагрузками. Проблема заключается в стабильности - выходное сопротивление op-amp объединяется с емкостью нагрузки, чтобы сформировать полюс, который вводит дополнительный фазовый сдвиг на 90 ° в функцию передачи петлевого усиления. Этот дополнительный фазовый сдвиг может привести к чрезмерному звонку или даже к колебаниям. (Моя группа отрицательных отзывов, в частности, часть 4 - часть 10, содержит множество информации об устойчивости, нестабильность, вызванную нагрузкой, обсуждается в части 9.). Вы можете посмотреть в таблице данных op-amp, чтобы получить представление о том, сколько емкость нагрузки, которую конкретное устройство может безопасно управлять; однако эта информация напрямую не применима к нашей схеме буферизации тока, поскольку емкость затвора MOSFET не подключена между выходным терминалом операционного усилителя и землей. Часть емкости (а именно, емкость затвора) подключается к земле через сопротивление нагрузки, и мы увидим, что это сопротивление серии влияет на стабильность схемы.

Зарядная или зарядная плата «затвор» более заметна, чем входная емкость. Это также относится к LTspice, который отображает только три параметра при открытии окна для выбора нового устройства NMOS или PMOS; одним из этих параметров является заряд затвора, и нет упоминания о емкости. Производители сосредотачиваются на заряде затвора, потому что это лучшая спецификация для расчета и сравнения скоростей переключения:

(время \ required \ to \ turn \ on \ MOSFET = \ frac {gate \ charge} {charge \ current} )

Для удобства я буду ссылаться на плату затвора, когда мне нужно передать входную емкость устройства по сравнению с другой MOSFET. Для наших целей достаточно понять, что больший заряд затвора соответствует большей емкости нагрузки. На самом деле нам не очень нужна фактическая емкость, потому что мы не будем пытаться аналитически прогнозировать фазовый запас или процент перерегулирования. Собственно, это подводит меня к следующему пункту. Полное описание: Сложность этой схемы: вольт-амперные характеристики полевого транзистора, различные паразитные емкости, выходное сопротивление op-усилителя, влияние разного сопротивления нагрузки, превосходят мою способность точно понимать и объяснять, что происходит в контекст стабильности. Я могу с уверенностью сказать, что большая емкость затвора может сделать схему менее стабильной, поэтому будьте осторожны. Также можно с уверенностью сказать, что, как правило, более низкое сопротивление нагрузки приводит к большей нестабильности. Помимо этого, я рекомендую вам симулировать и надеяться, что имитации, по крайней мере, будут соответствовать действительности.

базисный

Мы рассмотрим эту тему, посмотрев несколько иллюстративных сюжетных графиков. Для получения дополнительной информации об использовании шага для оценки стабильности см. Отрицательная обратная связь, часть 10: Стабильность во временной области. Вы также можете выполнять моделирование стабильности в частотной области, «разбивая петлю»; это обсуждается в разделе «Отрицательная обратная связь», часть 9.

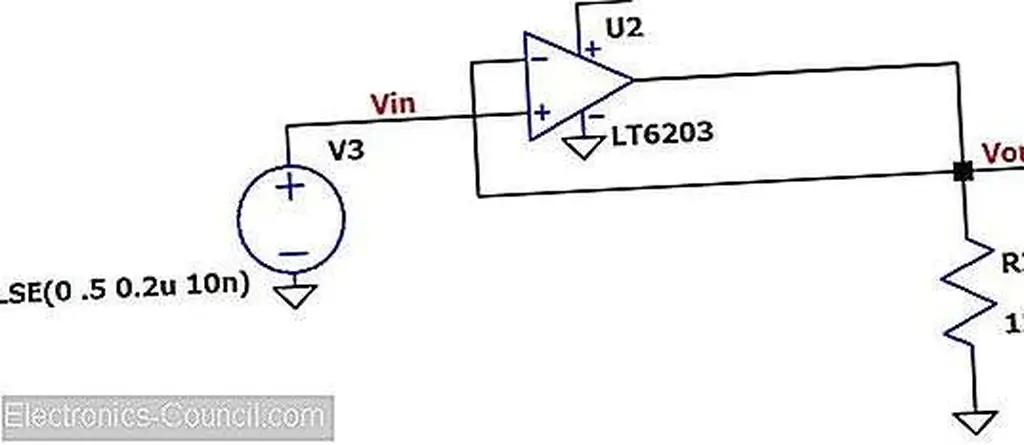

Начнем с ответа базового шага, т. Е. Того, как выглядит реакция шага без какого-либо буферного транзистора или емкости нагрузки. Вот схема:

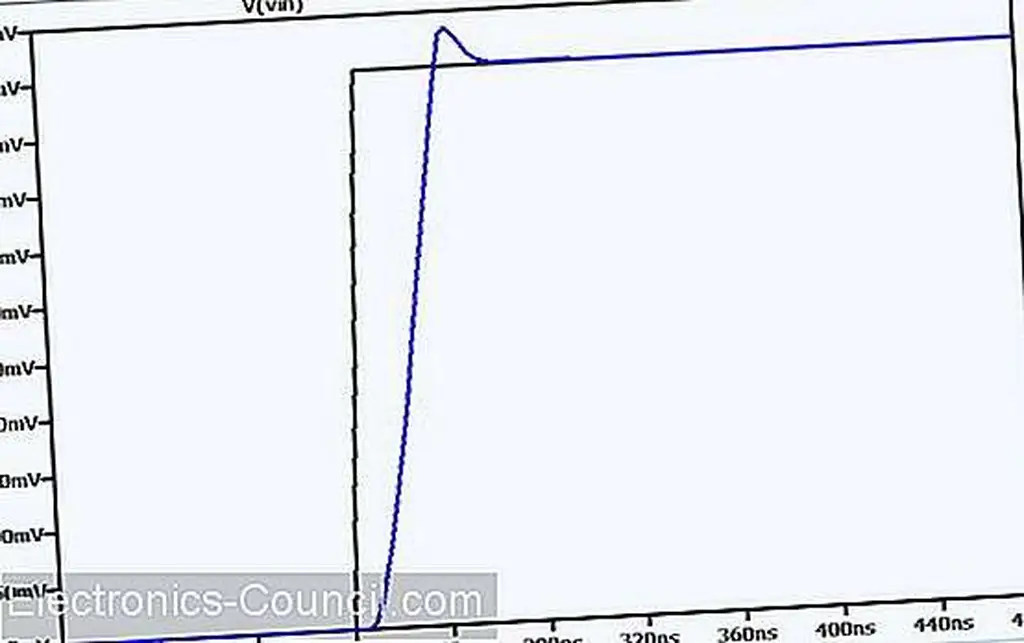

Резистор нагрузки выбирался на основе типичного максимального выходного тока LT6203, а именно 45 мА; вход представляет собой шаг 500 мВ и (500 мВ) / (45 мА) = 11, 1 Ом. Вот сюжет:

Задержка от входа к выходу отражает ограничение скорости нарастания ОУ, а умеренное превышение соответствует тому факту, что LT6203 имеет много фазового запаса при единичном усилении.

Перегрузка, Звонок, Колебание

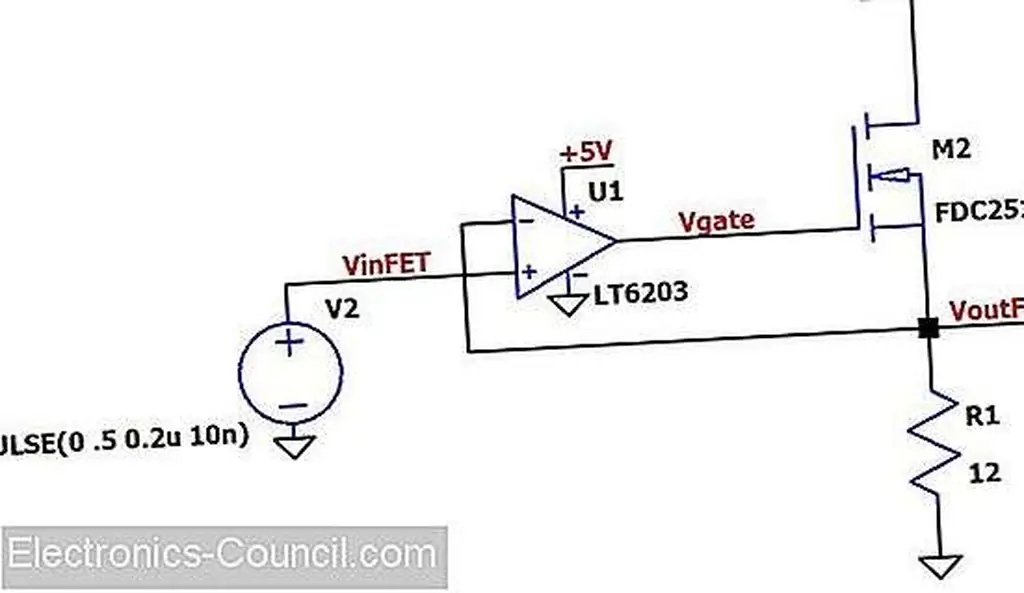

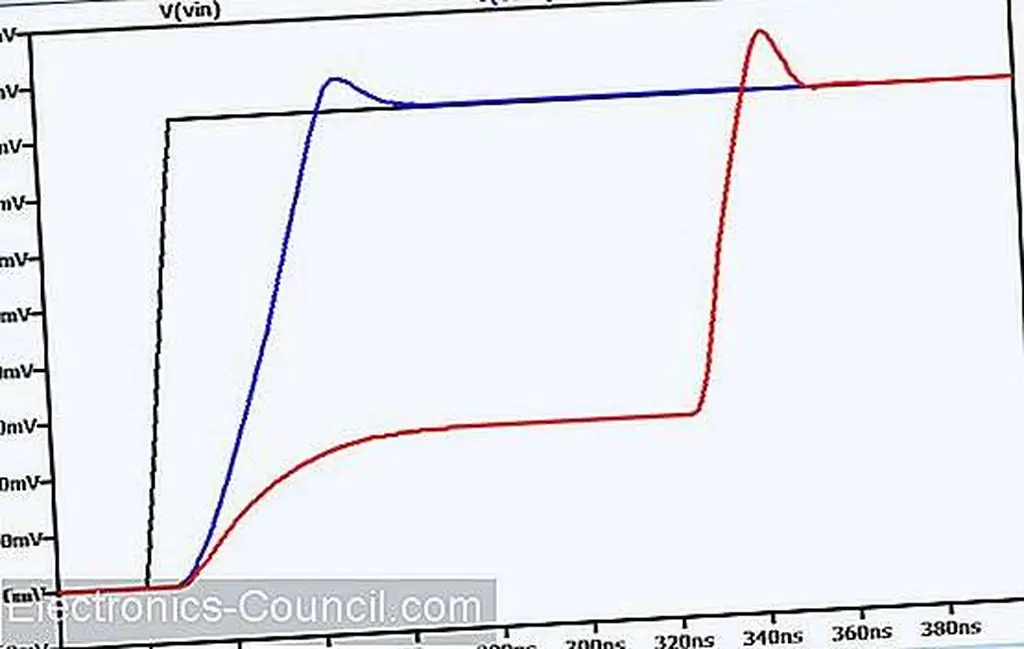

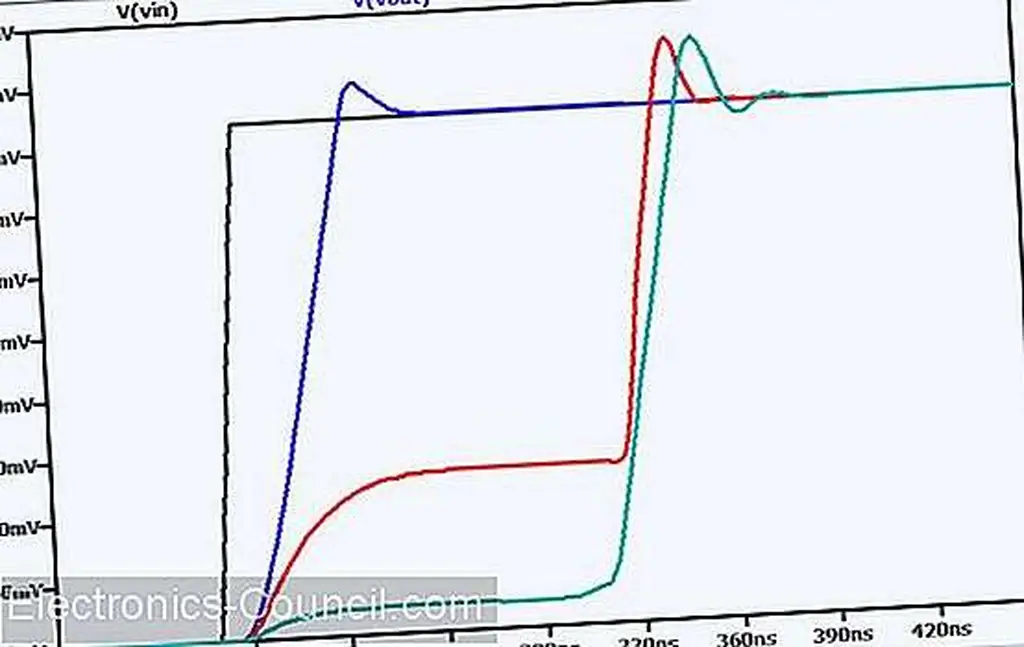

Теперь давайте вставим NMOS FDC2512 (заряд затвора = 8 нК) и посмотрим, что произойдет.

Амплитуда превышения увеличилась, и мы можем различить небольшую колебательную тенденцию. Тем не менее, этот шаг ответ ни о чем не беспокоит. Следующий график показывает эффект уменьшения сопротивления нагрузки от 12 Ом до 2 Ом.

Мы наблюдаем некоторое дополнительное колебательное поведение с более низким сопротивлением нагрузки, но амплитуда перерегулирования (около 60 мВ, или 12%) указывает на то, что схема все еще достаточно стабильна (12% превышения соответствует фазовому пределу около 57 °).

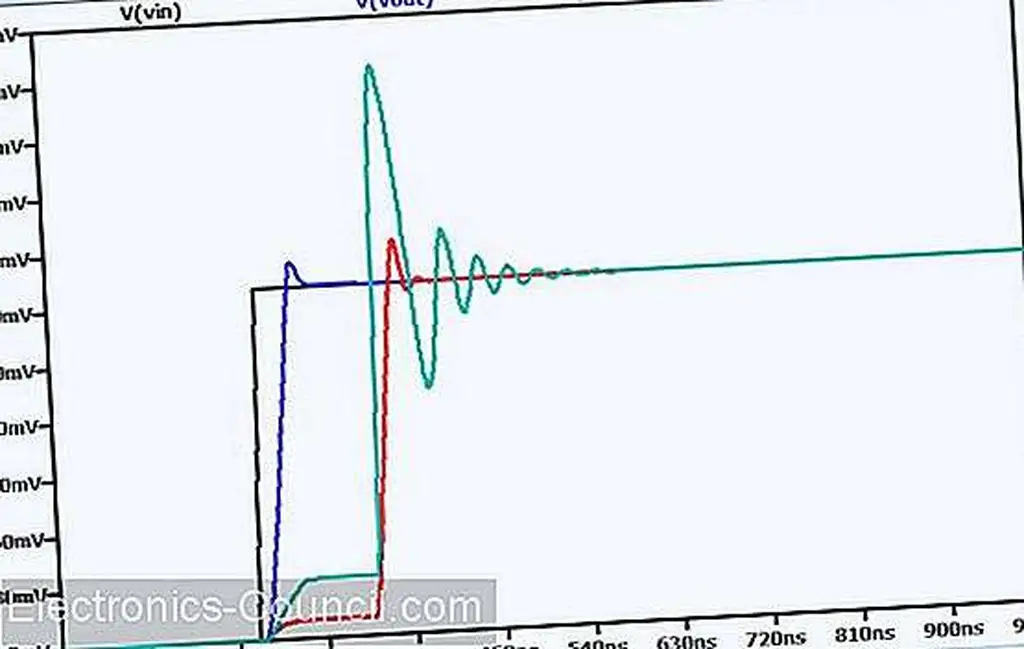

Теперь давайте сменим полевой транзистор на часть с большей емкостью затвора. Этот график включает результаты для FDS5680, который имеет плату затвора 30 нК, по сравнению с 8 нК с FDC2512. Сопротивление нагрузки для обоих цепей FET составляет 2 Ом.

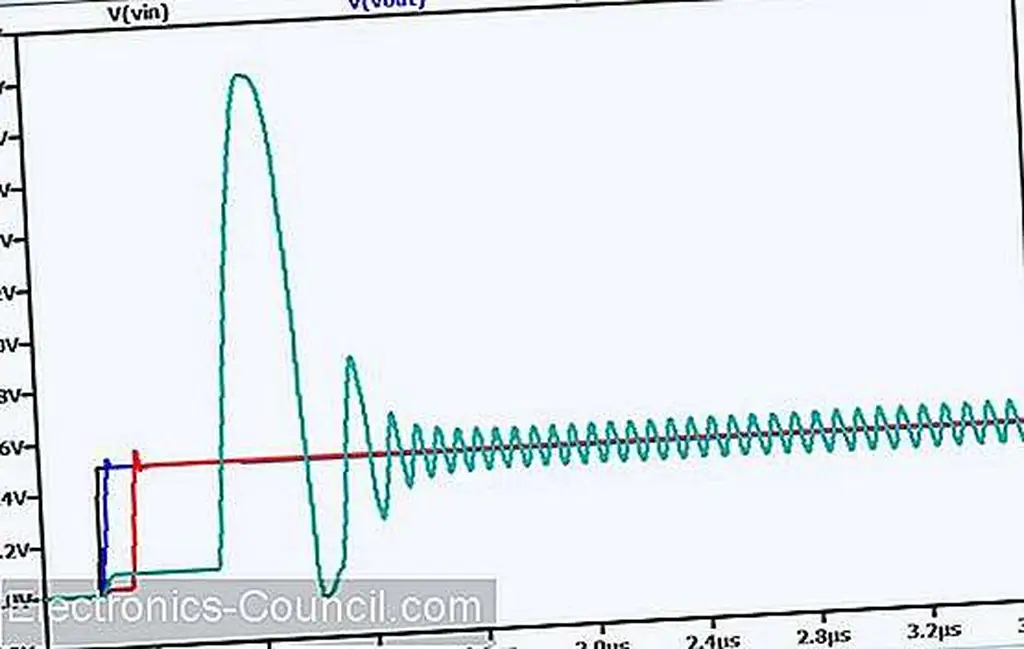

Очевидно, у нас есть проблема. Наш процент перерегулирования увеличился примерно до 60%, что означает, что запас по фазе составляет около 15 °, даже не близко к 45 °, необходимых для обеспечения достаточной стабильности. Именно поэтому мы можем оценить колебательную энергию, вызванную большой дозой нагрузки, вот результаты для FDB8030L (заряд затвора = 120 нК):

BJTs имеют емкость слишком

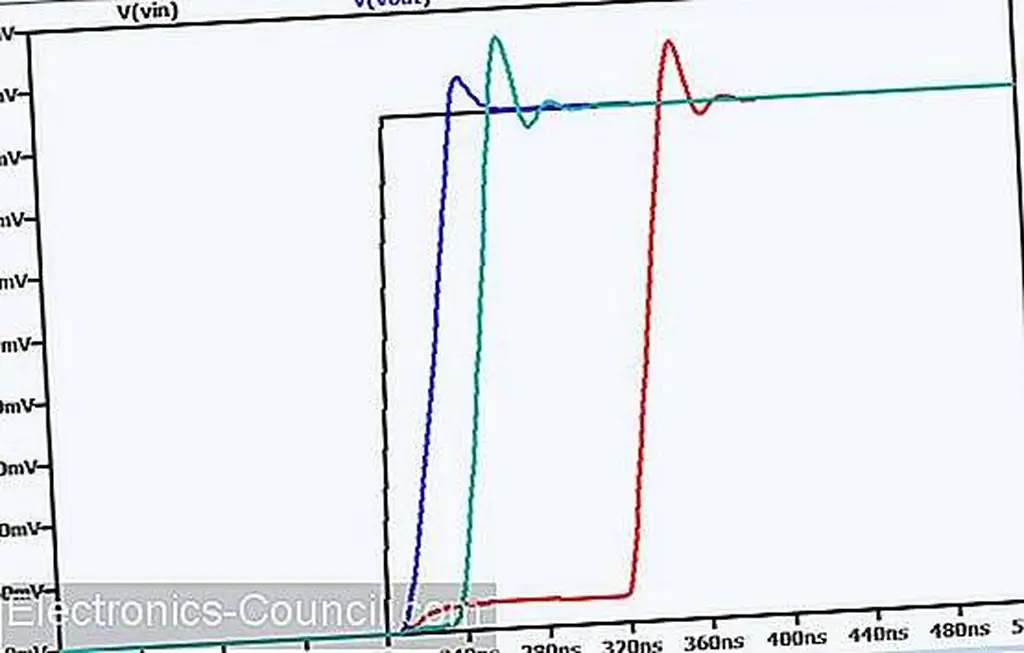

Вышеупомянутая демонстрация не означает, что полевые транзисторы повсеместно хуже, чем BJT, в контексте неустойчивости, вызванной нагрузкой. Я признаю, что я не пользуюсь MOSFET, когда дело доходит до буферизации выходного тока операционного усилителя, а не только потому, что в BJT есть что-то приятное старомодное. Дело в том, что мне не нравится беспокоиться о стабильности больше, чем я, и поэтому я предпочитаю избегать емкости затвора MOSFET. Однако приведенные выше результаты для FDC2512 (заряд затвора = 8 нC) указывают на то, что вы можете поддерживать адекватную стабильность, выбирая подходящую деталь (особенно учитывая, что вы можете получать высоковольтные полевые транзисторы с затвором затвора значительно ниже 8 нК). Кроме того, BJT приносят свою собственную емкостную нагрузку в виде pn- емкостной емкости. Взгляните на следующий график, который показывает результаты для FET2512 FET и 2SCR293P BJT (оба с R LOAD = 2 Ω).

Мы видим, что влияние BJT на стабильность ни в коем случае не является незначительным; на самом деле, превышение в трассе BJT немного хуже, чем на трассе FET.

Вывод

Оба MOSFET и BJT способствуют емкости нагрузки, что может ухудшить стабильность схемы ОУ с отрицательной обратной связью. Но вам нужно быть особенно осторожным с емкостью затвора MOSFET, которая в целом выше входной емкости BJT и значительно варьируется от части к части. Первоначально я думал, что добавление некоторого сопротивления серии между выходным терминалом операционного усилителя и воротами полевого транзистора уменьшит проблемы стабильности, но мои симуляции показали, что этот подход неэффективен (на самом деле последовательное сопротивление ухудшало колебания). Моя рекомендация состоит в том, чтобы искать детали с низким уровнем заряда, а затем использовать симуляции, чтобы гарантировать, что комбинация op-amp / MOSFET обеспечивает достаточную стабильность.