Как буферизовать выход Op-Amp для более высокого тока, часть 3

В предыдущих двух статьях основное внимание уделялось биполярным переходным транзисторам. В этой статье мы рассмотрим буферизацию с помощью MOSFET вместо BJT.

Вспомогательная информация

- Введение в операционные усилители

- Аудиоусилитель класса B

- Полевые транзисторы с изолированным затвором (MOSFET)

Предыдущие статьи в этой серии

- Как буферизовать выход Op-Amp для более высокого тока, часть 1

- Как буферизовать выход Op-Amp для более высокого тока, часть 2

BJT против MOSFET: постоянное соперничество

Я часто желаю, чтобы был краткий, окончательный ответ на старый вопрос: «Что лучше, BJT или MOSFET». Но, как вы, наверное, знаете, это похоже на вопрос: «Что лучше, автомобили или грузовики?» С обоими вопросами нет универсального ответа; скорее, детали каждой ситуации определяют, какой вариант является предпочтительным. В этой статье мы рассмотрим использование MOSFET в конкретном контексте буферизации вывода операционного усилителя для более высокого тока, и в процессе мы сможем сформировать общее представление о том, когда МОП-транзисторы могут быть предпочтительнее BJT, и наоборот,

Краткий обзор

Сначала давайте рассмотрим некоторые характерные характеристики MOSFET.

- Ток, протекающий через канал MOSFET, почти полностью контролируется напряжением затвора к источнику питания, когда полевой транзистор работает в активной области (aka saturation); в линейной (акотриодной) области ток зависит также от напряжения стока от источника.

- МОП-транзистор начинает ток, когда напряжение затвор-источник превышает пороговое напряжение. Количество тока (в активной области) пропорционально квадрату напряжения перегрузки, которое определяется как напряжение затвор-источник за вычетом порогового напряжения.

- Затвор MOSFET изолирован от остальной части устройства, так что установившийся ток, текущий в затвор, почти равен нулю. Я говорю «почти нулевое», потому что ток утечки протекает через диэлектрик затвора; для наших целей этот ток утечки пренебрежимо мал, хотя это проблема с чрезвычайно тонкими (т. е. менее 2 нм) затворными диэлектриками, используемыми в современных интегральных схемах.

- Физическая структура затвора MOSFET приводит к относительно большой емкости - в контексте предмета этой статьи, возможно, в 5 раз выше входной емкости эквивалентного BJT.

NPN Out, NMOS In

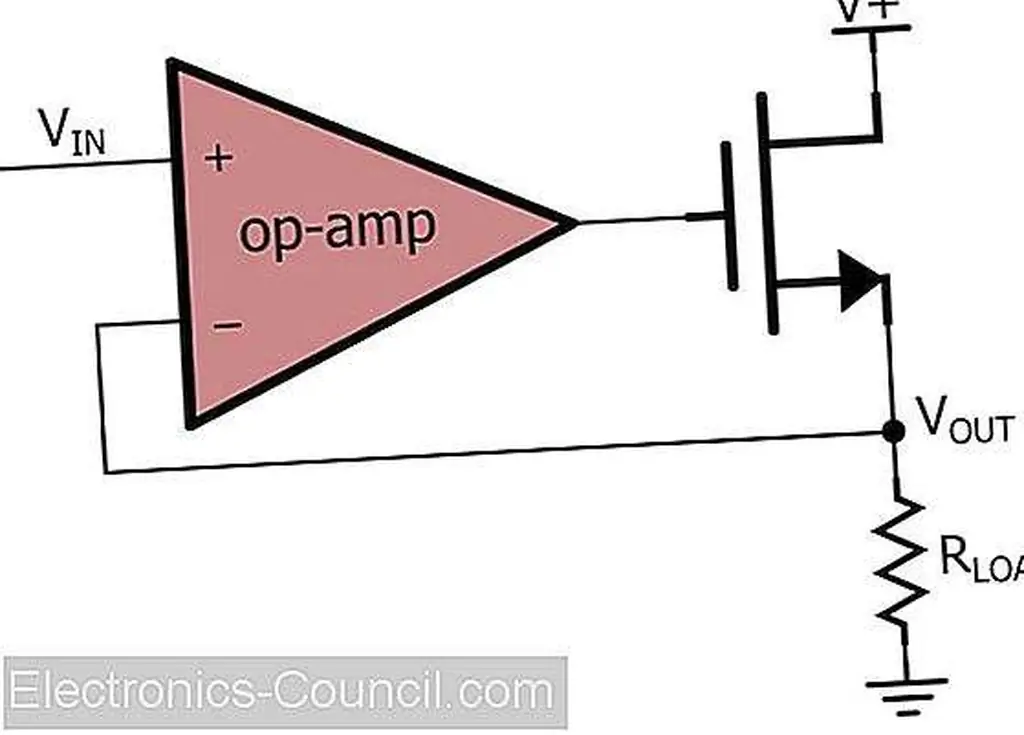

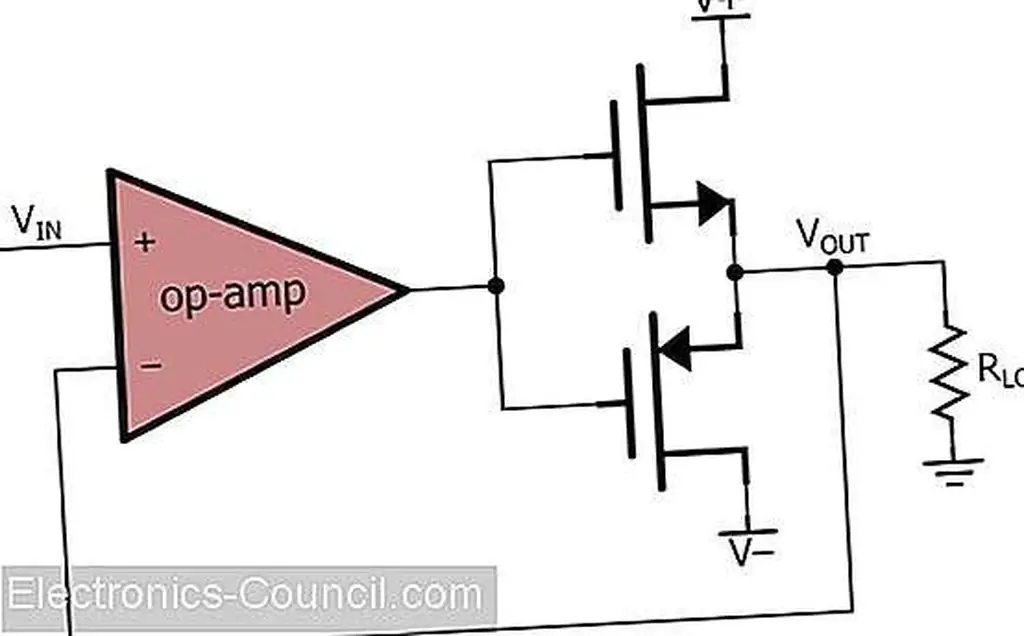

Вот первая конфигурация буферизации с MOSFET вместо BJT:

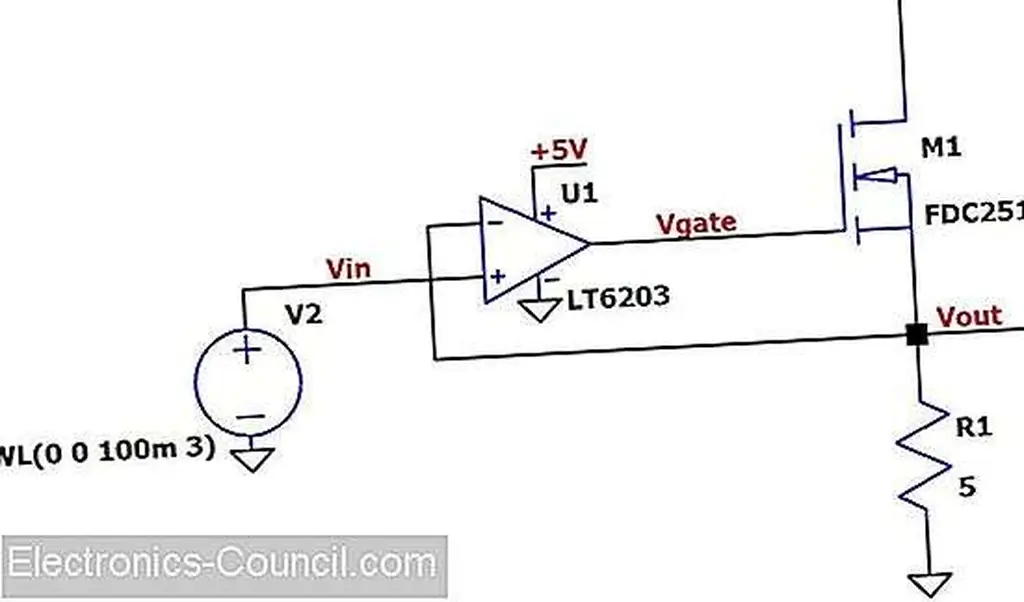

И вот схема LTspice:

Я выбрал часть NMOS на основе максимального тока стока; Я хотел что-то подобное по возможностям для NPN 2SCR293P, используемого в части 1, чтобы сравнение было более значимым. Максимальный ток непрерывного коллектора 2SCR293P составляет 1 А, а максимальный непрерывный ток стока для FDC2512 равен 1, 4 А. Две части также имеют одинаковые пределы рассеивания мощности. Как и ожидалось, существует значительная разница в входной емкости: для 2SCR293P, около 90 пФ; для FDC2512, около 375 пФ.

Пороговое напряжение

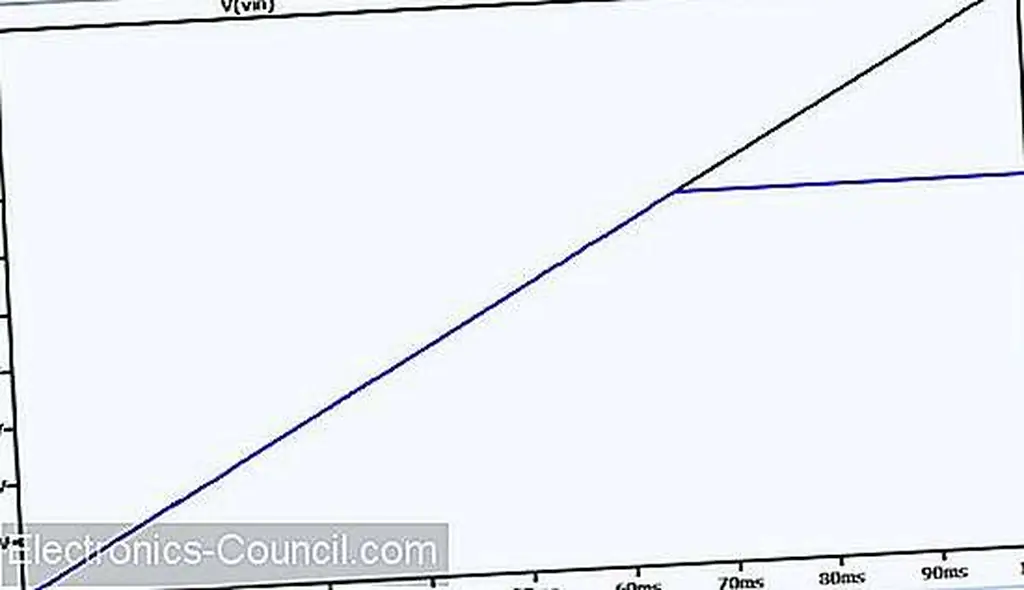

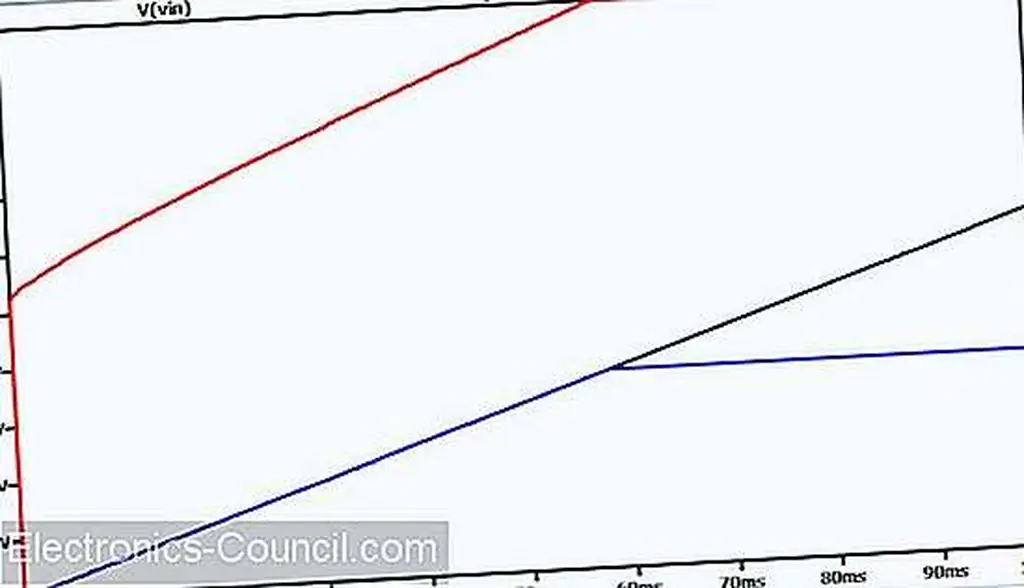

Вот график с V IN и V OUT.

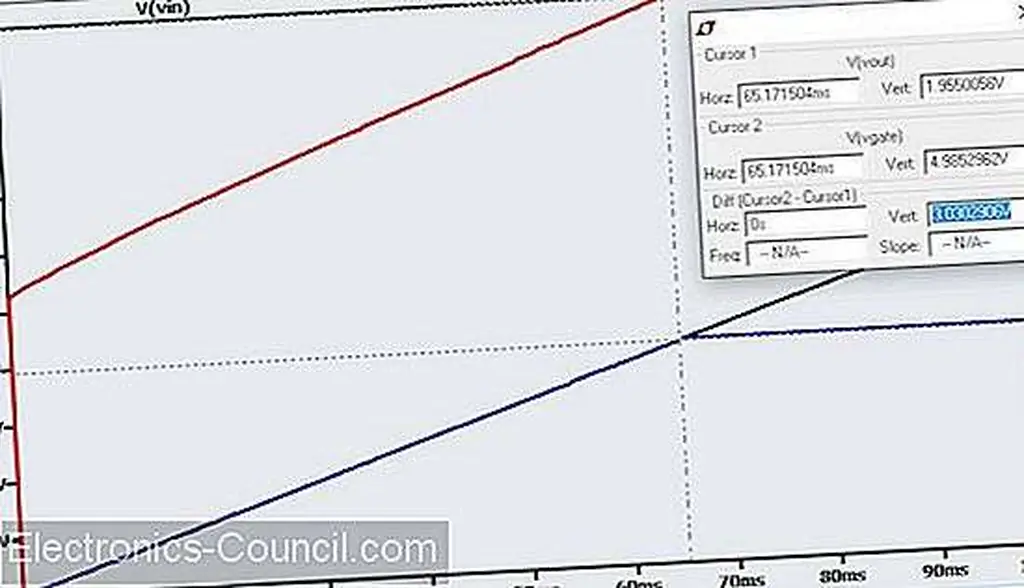

Проблема сразу же проявляется: напряжение нагрузки достигает уровня менее 2 В, хотя у нас есть 5 В для NMOS и операционного усилителя. Следующий сюжет показывает причину.

Как вы можете видеть, напряжение затвора насыщается при положительном напряжении питания ОУ, когда напряжение нагрузки составляет всего около 2 В. Основная проблема здесь заключается в пороговом напряжении МОП-транзистора: полевой транзистор даже не начинает проводить до тех пор, Напряжение источника-источника составляет 2, 6 В. Это означает, что выходное напряжение ОУ будет всегда на 2, 6 В выше напряжения нагрузки, поскольку разность напряжений будет только возрастать по мере того, как требуется больше тока стока - как показано на предыдущем графике, напряжение затвор-источник составляет 3 В, когда выходной уровень отключается. Фактически, напряжения, показанные на графике, представляют типичные характеристики FDC2512; согласно техническому описанию, пороговое напряжение может достигать 4 В!

Эта первая симуляция демонстрирует главный недостаток использования NMOS-транзистора в этой схеме: пороговое напряжение намного выше, чем 0, 7-0, 9 В, необходимое для перехода на базовый эмиттер NPN. Конечно, пороговое напряжение меняется от части к части, поэтому вы, безусловно, можете смягчить эту проблему, выбрав другой FET. Быстрый поиск по Digi-Key указывает на то, что NMOS-транзисторы, рассчитанные на ток непрерывной слива 1-2 А, могут иметь пороговое напряжение намного ниже, чем 2, 6 В. Тем не менее, вы должны быть осторожны здесь, потому что пороговое напряжение NMOS имеет тенденцию быть выше, чем 0, 7- 0, 9 В от базового к эмиттеру, которое можно ожидать от практически любого NPN-транзистора. Даже пара Дарлингтона (обсуждаемая в части 2) обеспечит диапазон напряжения нагрузки, близкий или превосходящий то, что вы получите от некоторых полевых МОП-транзисторов, а Дарлингтон уменьшит ток базы до уровней, которые могут обрабатывать практически любые операционные усилители.

Еще одна деталь, о которой следует помнить, заключается в следующем: диапазон напряжения нагрузки становится более ограниченным с большими токами нагрузки, потому что операционный усилитель должен создавать более высокое напряжение перегрузки для получения более высокого тока стока. Если мы установим нагрузочный резистор на 2 Ω вместо 5 Ω, мы получим следующий график:

В этом случае напряжение нагрузки уменьшается примерно на 1, 75 В вместо 2 В.

Поглощение и поиск

Это обсуждение NMOS-транзистора имеет отношение также к PMOS-транзистору, который вы использовали бы в качестве токоограничивающего устройства в выходном каскаде класса B (см. Часть 2).

Производительность этапа NMOS-PMOS будет сопоставима с этапом этапа NPN-PNP; просто убедитесь, что вы тщательно выбираете свои полевые транзисторы для обеспечения достаточно низкого порогового напряжения.

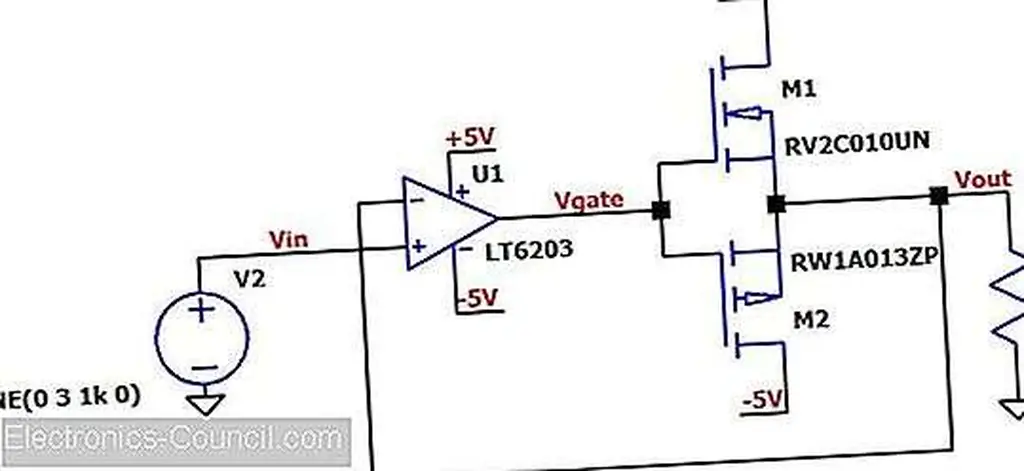

Вот схема LTspice:

У меня возникли проблемы с поиском подходящих деталей среди встроенных функций NMOS и PMOS LTspice, поэтому вместо этого я использую две модели FET с низким пороговым напряжением от ROHM Semiconductor. NMOS - номер детали RV2C010UN, а PMOS - номер детали RW1A013ZP. Ссылки, прикрепленные к этим номерам, приведут вас к страницам продуктов, на которых вы можете загрузить модель SPICE (справа под «ТЕХНИЧЕСКИЕ ДАННЫЕ»), и вы можете перейти сюда для объяснения того, как использовать стороннюю модель с LTSpice NMOS и PMOS.

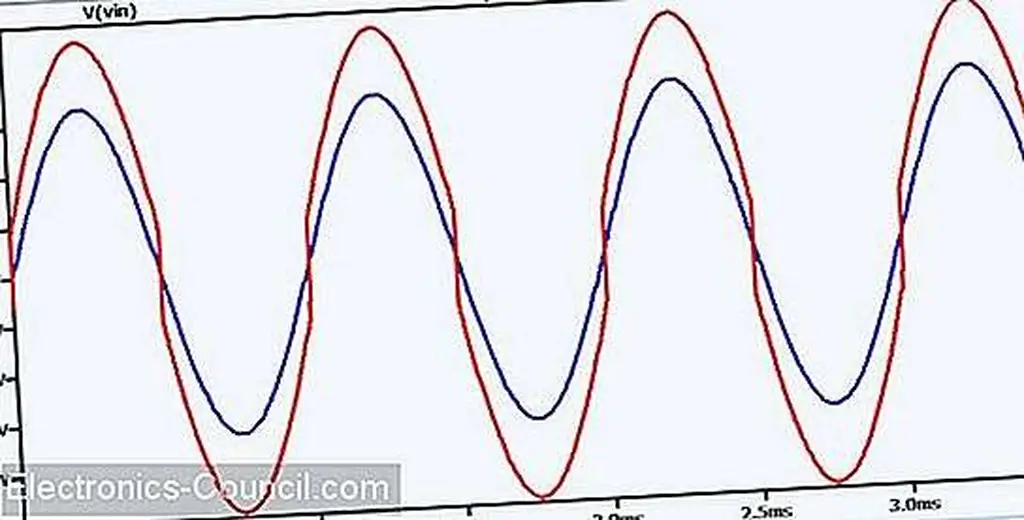

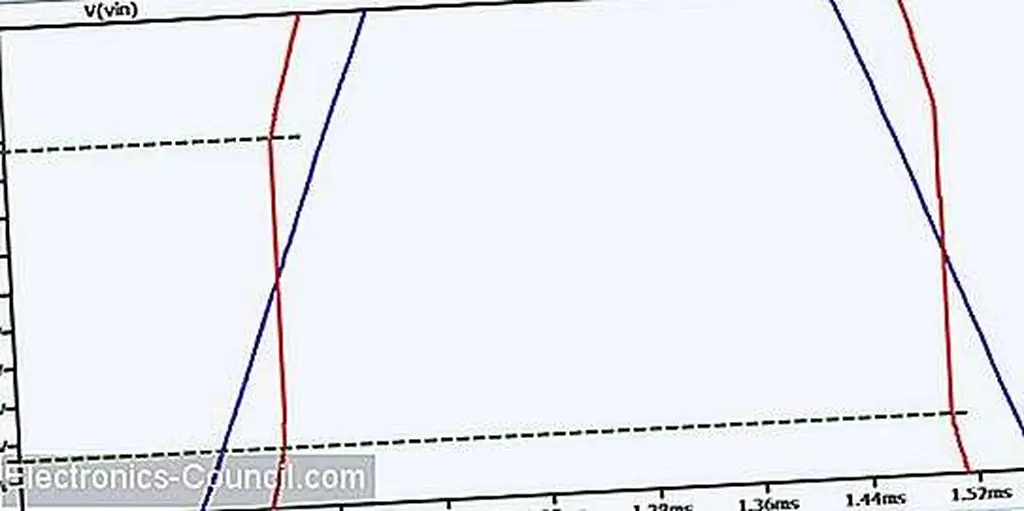

Вот график с V IN, V OUT и V GATE:

V IN скрыт под V OUT. Как и в случае с версией BJT, выходное напряжение ОУ (т. Е. V GATE) обходит мертвую зону, в которой оба полевых транзистора отключены. Кроме того, этот график отлично подходит для визуализации того, как разница между V GATE и V OUT увеличивается, поскольку V OUT (и, следовательно, ток нагрузки) увеличивается; это отражает основную работу активного режима полевого МОП-транзистора, а именно, более высокий ток стока требует большего напряжения перегрузки.

Если мы увеличим масштаб, мы увидим, что пороговое напряжение для NMOS и PMOS составляет около 0, 75 В и 0, 9 В соответственно. Таким образом, с этими конкретными частями пороговое напряжение не намного выше, чем падение напряжения BJT от источника к эмиттеру.

Вывод

Базовые схемы буферизации базового ОУ могут хорошо работать как с BJT, так и с МОП-транзисторами. Основным преимуществом МОП-транзистора является незначительный выходной ток, требуемый от ОУ, и основная проблема заключается в том, что диапазон выходного напряжения может быть ограничен относительно высокими напряжениями от источника к источнику. В следующей статье мы рассмотрим тонкую, но значительную проблему, которая может усложнить использование MOSFET для буферизации текущих операционных усилителей: влияние емкости затвора на стабильность.

Следующая статья в серии: как буферизовать выход Op-Amp для более высокого тока, часть 4