Базовая дифференциальная пара MOSFET

В этой статье мы рассмотрим наиболее простую версию этой топологии базового интегрального интегратора.

Вспомогательная информация

- Дискретные полупроводниковые схемы: дифференциальный усилитель

- Дискретные полупроводниковые схемы: простой Op-Amp

- Изолированные транзисторы с полевым эффектом (MOSFET)

Differential или Single-Ended "// www.allaboutcircuits.com/technical-articles/negative-feedback-part-1-general-structure-and-essential-concepts/" target = "_ blank"> Отрицательная серия отзывов, вы знаете, что отрицательная обратная связь - это лучшее, что может случиться с схемой усилителя.

Разумно ожидать, что эти преимущества будут сопровождаться значительными недостатками, но характер изготовления ИС делает дифференциальную конфигурацию практически полезной. Две проблемы: 1) превышение количества компонентов и 2) важность характеристик симметричных компонентов. Вы можете забыть о номере 1, потому что стоимость добавления нескольких транзисторов в IC незначительна. Что касается номера 2, технология ИС очень хороша в достижении согласованности между компонентами в чипе (эта согласованность называется «сопоставление»).

В этой статье мы рассмотрим базовую конфигурацию дифференциального усилителя MOSFET с помощью концептуального обсуждения и моделирования (т. Е. Не слишком много математического или сложного анализа схемы). Поскольку этот вопрос относится в первую очередь к реализации ИС, мы будем использовать модель NMOS, которая является специфичной для CMOS-технологии 0, 35 мкм; различные файлы LTspice и некоторую связанную информацию можно найти здесь.

Пара МОП-транзисторов

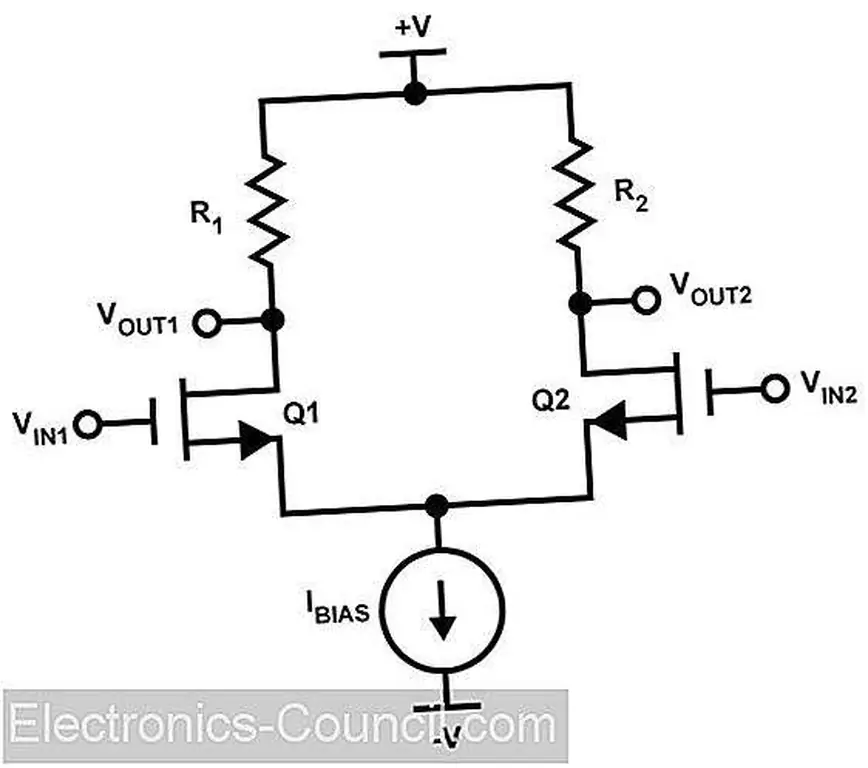

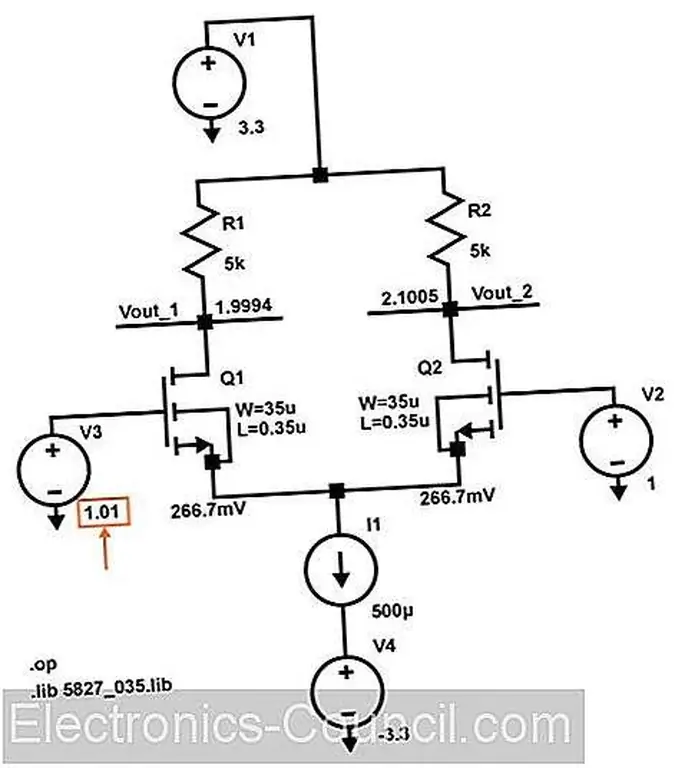

Это схема:

Обратите внимание на следующее:

- В реальной жизни символ источника тока будет заменен схемой, которая генерирует постоянный ток. (Обратитесь к основному источнику постоянного тока MOSFET для получения дополнительной информации.) Однако мы хотим сохранить все хорошо и просто для этого вводного анализа, поэтому в наших симуляциях мы будем использовать идеальный источник тока вместо схемы с постоянным током.

- Фактическая реализация ИС этой схемы заменила бы резисторы текущим зеркалом, функционирующим как «активная нагрузка». Однако, если наша цель - понять функциональность дифференциальной пары, я думаю, что мы должны начать с версии резистора.

- Дифференциальная пара - это баланс. Таким образом, для оптимальной работы необходимо согласовать резисторы и МОП-транзисторы. Это означает, что размеры каналов обоих полевых транзисторов должны быть одинаковыми, а R 1 должен равняться R 2. Значение сопротивления, выбранное для двух резисторов, будет называться R D (для сопротивления сливу).

Анализ DC

Определим условия смещения этой схемы, когда оба входа заземлены.

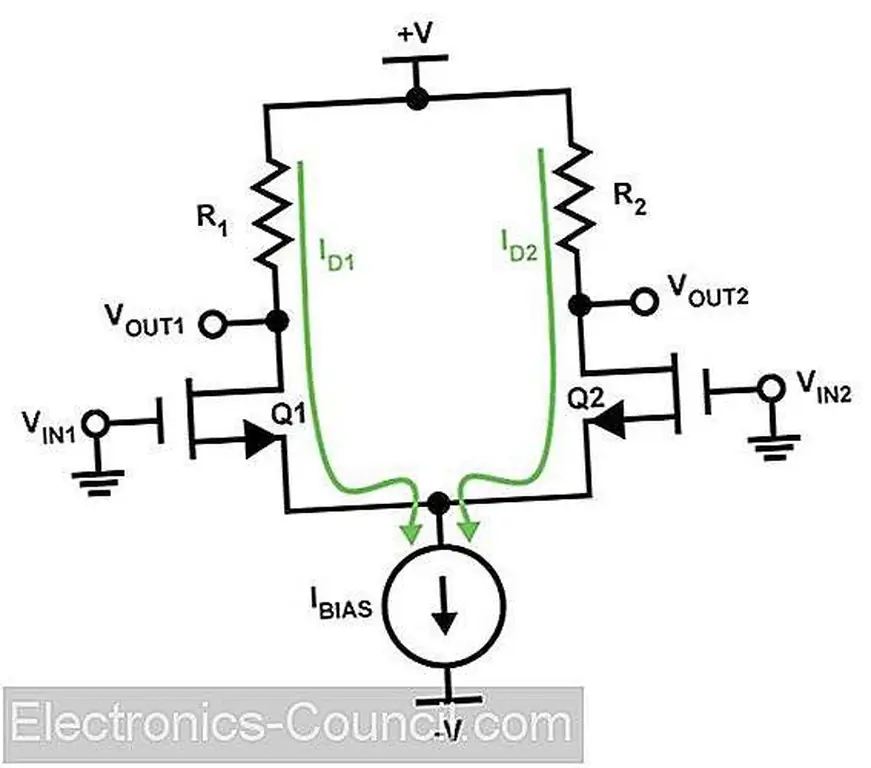

Сумма двух токов стока I D1 и I D2 должна равняться I BIAS. Мы также знаем, что два тока стока равны, потому что в этом идеализированном анализе обе половины цепи идентичны. Таким образом, (I_ {D1} = I_ {D2} = {гидроразрыва I_ {ПРЕДУБЕЖДЕНИЯ}} {2} )

Предположим на данный момент, что транзисторы находятся в насыщении. Уравнение для тока стока насыщающего режима следующее:

(I_D = \ гидроразрыва {1} {2} mu_nC_ {вола} гидроразрыва {W} {L} (V_ {} Г. С. -V_ {TH}) ^ 2 )

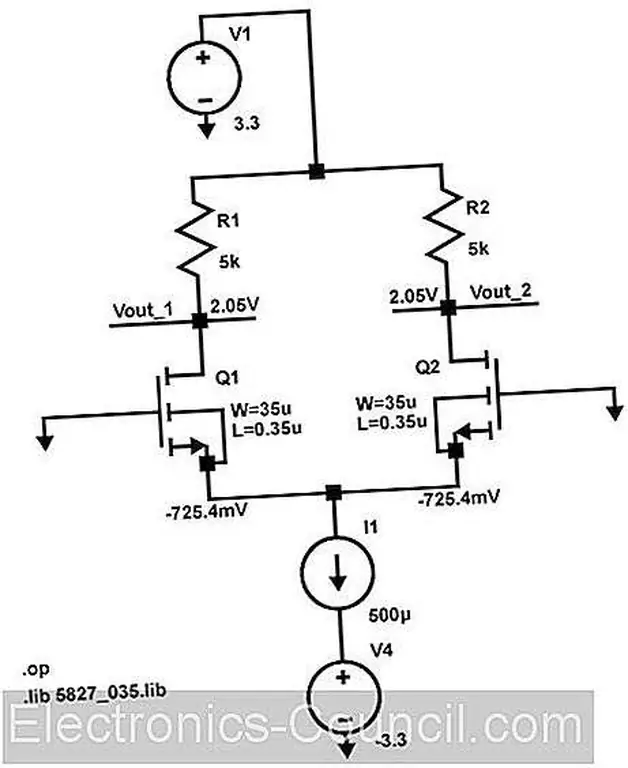

(Мы будем игнорировать модуляцию длины канала в этой статье.) Ток стока уже установлен (источником тока), а ворота привязаны к наземному узлу; это означает, что напряжение источника будет опираться на любое значение, создающее напряжение затвора от источника (V GS), соответствующее току стока I BIAS / 2. Мы дадим симулятору понять это для нас. Напряжения на выходе проще: рассчитайте падение напряжения на резисторе как (I BIAS / 2) × R D, затем вычтите это падение напряжения от положительной подачи. Вот пример:

Выходные напряжения соответствуют ожиданиям. Напряжение источника кажется разумным, учитывая, что пороговое напряжение (V TH) для этой модели SPICE составляет около 0, 5 В; симуляция говорит нам, что V GS, соответствующий току стока 250 мкА, составляет около 0 В - (-725 мВ) = 725 мВ, что составляет около 225 мВ выше V ГТ.

Вернемся к нашему предположению о том, что транзисторы находятся в насыщении (он же «активный режим»). Усилитель MOSFET должен оставаться в части насыщения передаточной характеристики, поскольку коэффициент усиления выше и более стабилен в области насыщения по сравнению с триодной областью. Для обеспечения насыщения напряжение стока должно всегда быть выше напряжения затвора минус пороговое напряжение:

(V_ {DS} geq V_ {GS} -V_ {TH} \ \ Rightarrow \ \ V_ {GD} leq V_ {TH} )

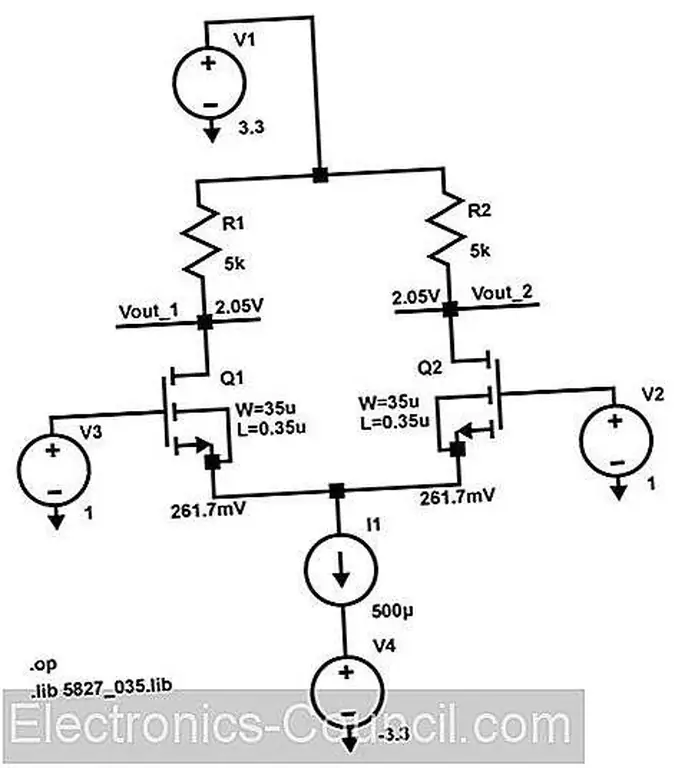

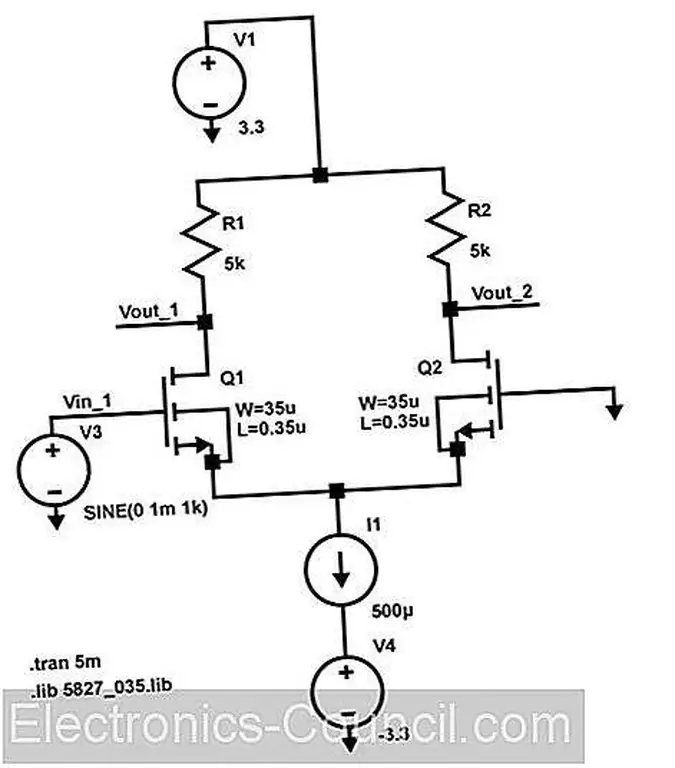

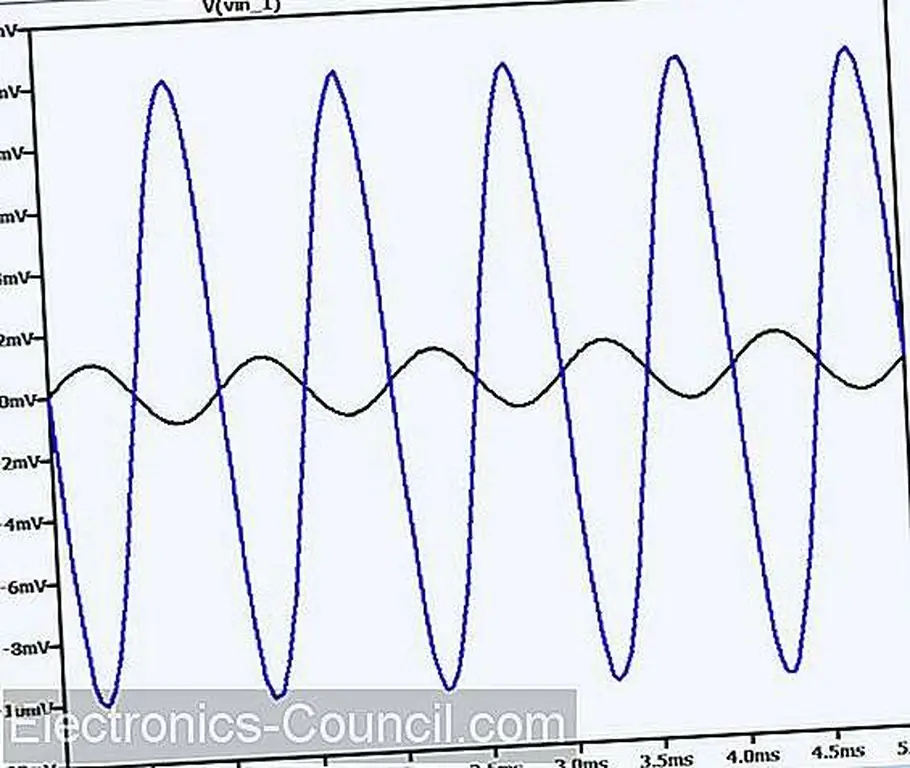

В этом примере напряжение стока (aka V OUT) фиксировано при 2, 05 В. Это означает, что у нас есть ограничение на V IN: входное напряжение синфазного сигнала не может превышать 2.05 В + 0.5 В = 2.55 В, потому что, когда вход напряжение достигает V TH вольт над напряжением стока, MOSFET входит в зону триода. Давайте сделаем быстрое симуляцию, чтобы доказать себе, что дифференциальная пара не будет усиливать синфазные напряжения. Вот схема: Как вы можете видеть, даже при вхождении в единый режим 1 В выходное напряжение все еще находится в напряжении смещения -2, 05 В. Простым концептуальным объяснением этого поведения отказа синфазного режима является следующее: Величина выходного напряжения регулируется током стока, а не входным напряжением. Пока два входных напряжения одинаковы, фиксированный ток смещения равномерно распределяется между двумя транзисторами, и поэтому V OUT1 и V OUT2 не меняются. Обратите также внимание на то, что напряжение затвор-источник примерно одинаковое (поскольку ток стока не изменился), хотя напряжение источника увеличилось, чтобы компенсировать тот факт, что ворота теперь находятся на уровне 1 В вместо земли. Вы можете понять дифференциальное действие этой схемы, если вы помните следующее: Если напряжение на затворе Q 1 выше напряжения на затворе Q 2, V GS1 также должно быть выше V GS2, поскольку оба транзистора имеют одинаковый потенциал на клемме источника. Более высокое напряжение от источника к источнику означает больший ток стока, но сумма токов стока остается одинаковой - таким образом, I D1 увеличивается, а I D2 уменьшается, и это вызывает соответствующее уменьшение V OUT1 и соответствующее увеличение V OUT2, Например: Мы закончим этот вводный анализ, моделируя дифференциальный сигнал с малым сигналом и сравнивая имитированный коэффициент усиления с теоретическим коэффициентом усиления. Возьмем напряжение синфазного напряжения до 0 В, а затем применим синусоидальную волну 1 мВ к затвору Q 1: Мы будем определять выходное напряжение как V OUT1 - V OUT2; это удваивает коэффициент усиления относительно использования только V OUT1 или V OUT2, а также устраняет смещение постоянного тока, связанное с напряжениями смещения. Вот график с V IN1 и дифференциальным выходным напряжением: Здесь мы имеем выходную амплитуду 10 мВ и входную амплитуду 1 мВ; следовательно, наш имитированный дифференциальный коэффициент усиления равен 10. Формула для теоретического дифференциального коэффициента усиления равна (A_ {diff} = g_m \ times R_D ) где g m можно рассчитать следующим образом: (G_m = \ SQRT {2 \ mu_nC_ {вола} влево ( гидроразрыва {W} {L} справа) I_D} = \ SQRT { mu_nC_ {вола} влево ( гидроразрыва {W} {L} справа) I_ {BIAS}} ) Модель SPICE имеет μ n = 148, 2 см 2 / В · с и t ox = 7, 754 × 10 -9. Мы можем рассчитать C ox как (C_ {ox} = \ frac { epsilon_ {ox}} {t_ {ox}} = \ frac {3.45 \ times10 ^ {- 11} \ frac {F} {m}} {7.754 \ times 10 ^ {-9} m} = 4.449 \ times10 ^ {- 3} \ frac {F} {m ^ 2} ) Таким образом, ( mu_nC_ {ox} = 148.2 \ \ frac {cm ^ 2} {V \ cdot s} times \ left (4.449 \ times10 ^ {- 3} \ frac {F} {m ^ 2} right) = 65, 9 \ \ frac { mu A} {V ^ 2} ) Почти готово: (g_m = \ sqrt {65.9 \ \ frac { mu A} {V ^ 2} times \ left ( frac {35 \ \ mu m} {0.35 \ \ mu m} right) times500 \ \ mu A} = 0, 00182 \ \ frac {A} {V} ) Готово: (A_ {diff} = 0, 00182 \ \ frac {A} {V} times5 \ k \ Omega = 9.1 ) Вычислено = 9.1, имитировано = 10: Я бы сказал, что это довольно близко. Базовая дифференциальная пара MOSFET является важной схемой для всех, кто хочет вникать в аналоговую схему IC. Мы можем многое сказать об этой схеме, но сейчас мы ее оставим. В следующей статье мы рассмотрим улучшенную производительность, которая может быть достигнута за счет использования активной нагрузки вместо дренажных резисторов.Отказ от синфазного режима

Дифференциальное усиление

Вывод